# Logic and Computer Design Fundamentals Chapter 7 – Registers and Register Transfers Part 3 – Control of Register Transfers

### **Charles Kime**

© 2008 Pearson Education, Inc. (Hyperlinks are active in View Show mode)

# Overview

- Part 1 Registers, Microoperations and Implementations

- Part 2 Counters, Register Cells, Buses, & Serial Operations

- Part 3 Control of Register Transfers

- Introduction to register transfer systems

- Register transfer system design procedure

- A design example

- Microprogrammed control

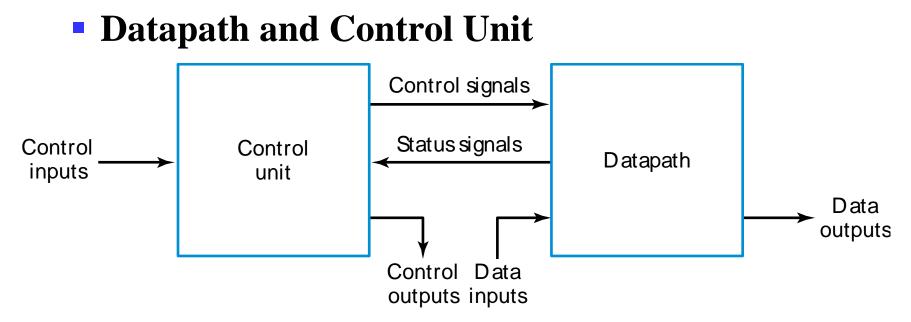

# **Introduction to Register Transfer Systems**

- Set of registers, mostly in Datapath with some in Control Unit

- Register transfers performed on registers

- Control that supervises the sequencing of the register transfers

# **Programmable and Non-Programmable Systems**

- Programmable System a portion of the input consists of a sequence of instructions called a *program*, typically stored in a memory and addressed by a *program counter (PC)*. The Control Unit is responsible for fetching and executing these instructions.

- Non-programmable System the control unit does not deal with fetching and executing instructions, but contains all of the information for sequencing register transfers based on inputs and on status bits from the datapath.

- Only non-programmable designs are considered here.

# **Register Transfer System Design Procedure**

- Write a detailed system specification

- Determine all data, control and status input signals, all data, control and status output signals, and registers of the datapath and control unit.

- Find a state machine diagram for the system including register transfers for the datapath and control unit as outputs.

- Determine all internal control and status signals. Use these signals to separate output conditions and actions, including register transfers, from the state machine diagram flow and represent them in tabular form.

- Draw a block diagram of the datapath including all control and status inputs and outputs. Draw a block diagram of the control if it includes register transfer hardware.

- Design any specialized register transfer logic as needed for the datapath and the control.

- Design the control unit logic.

- Verify the correct operation of the combined datapath and control unit. If verification fails, debug the system and verify the changed system.

# DASHWATCH

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 5 - Part 3 6

# **Example 1: DASHWATCH**

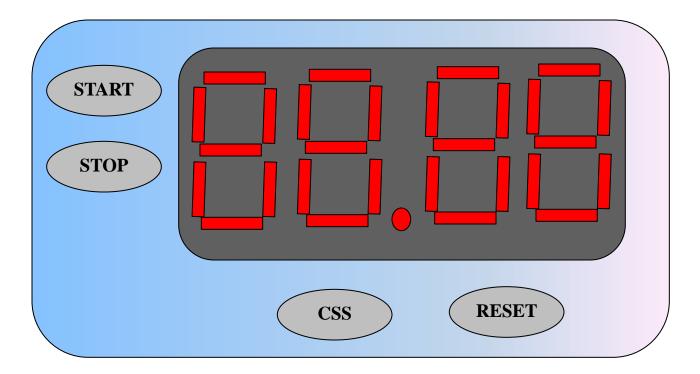

**Exterior View**

# Example 1 – DASHWATCH Specifications

- Very Inexpensive Stop Watch for "dash" runners

- Times intervals to at most 99.99 seconds

- Stopwatch action plus storage of best performance time per session (session ended by turning off power or pushing RESET)

- Inputs: START, STOP, CSS (compare and store shortest), RESET

- Registers: 4-digit BCD Counter (TM) and 16-bit Parallel Load Register (SD)

- Output: 4 digit BCD LCD with decimal point

# **Example 1: DASHWATCH Inputs, Outputs, and Registers**

### 🗖 TABLE 7-15

Inputs, Outputs, and Registers of the DashWatch

| Symbol   | Function                                                                                                   | Туре               |

|----------|------------------------------------------------------------------------------------------------------------|--------------------|

| STA RT   | Initialize timer to 0 and start timer                                                                      | Control input      |

| STOP     | Stop timer and display timer                                                                               | Control input      |

| CSS      | Compare, store and display shortest dash time                                                              | Control input      |

| RESET    | Set shortest value to 10011001                                                                             | Control input      |

| $B_1$    | Digit 1 data vector a, b, c, d, e, f, g to display                                                         | Data output vector |

| $B_0$    | Digit 0 data vector a, b, c, d, e, f, g to display                                                         | Data output vector |

| DP       | Decimal point to display (= 1)                                                                             | Data output        |

| $B_{-1}$ | Digit –1 data vector a, b, c, d, e, f, g to display                                                        | Data output vector |

| $B_{-2}$ | Digit –2 data vector a, b, c, d, e, f, g to display                                                        | Data output vector |

| B        | The 29-bit display input vector (B <sub>1</sub> , B <sub>0</sub> , DP, B <sub>-1</sub> , B <sub>-2</sub> ) | Data output vector |

| TM       | 4-Digit BCD counter                                                                                        | 16-Bit register    |

| SD       | Parallel load register                                                                                     | 16-Bit register    |

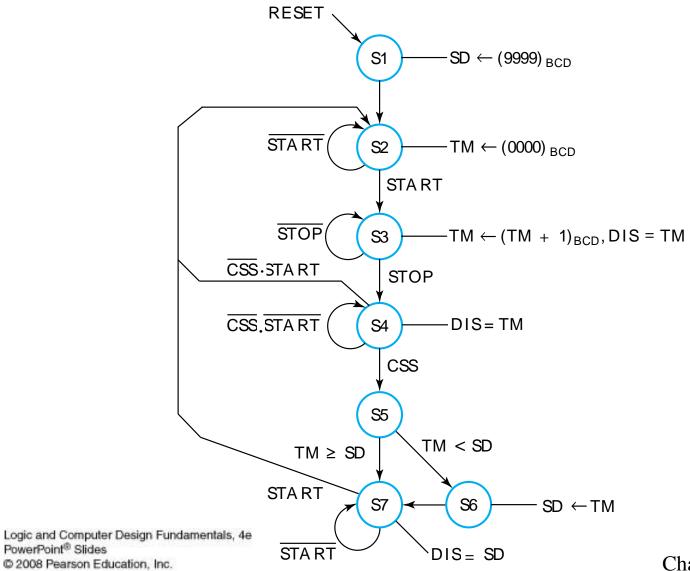

## **Example 1: DASHWATCH SMD with Register Transfer Outputs**

Chapter 7 - Part 3 10

# Example 1: DASHWATCH SMD Design

- Specify only Moore outputs (no particular reason)

- S1: Reset state in this state, initialize SD to 1001100110011001 (99.99), the maximum possible dash time.

- S2: Because of Moore output spec, S1 cannot be used for this state since SD is not to be initialized again to 99.99 after having passed through states S4 or S7. TM is initialized to (0000)<sub>BCD</sub> for next dash.

- S3: State during dash. Entered with START and exited with STOP. While in state, 1 (0.01 seconds) is added to TM for each clock pulse. (Clock frequency is 100 Hz), and DIS shows TM value.

- S4: Decision state whether to Compare, Store, and display Shortest dash time, or to continue to display TM. Also START begins new dash.

- **S5:** State for comparison of TM to SD.

- S6: State for loading TM into SD if TM is smaller.

- S7: State for START to begin new dash and display of SD as shortest dash time.

# **Example 1: DASHWATCH Output Control/Status Table**

#### **TABLE 7-16**

Datapath Output Actions and Status Generation with Control and Status Signals

| Action or Status                                                                 | Control or<br>Status<br>Signals | Meaning for Values 1 and 0                                                                                                         |

|----------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| TM $\leftarrow$ (0000) <sub>BCD</sub><br>TM $\leftarrow$ (TM + 1) <sub>BCD</sub> | RSTM<br>ENTM                    | 1: Reset TM to 0 (synchronous reset)<br>0: No reset of TM<br>1: BCD count up TM by 1, 0: hold TM value                             |

| SD ← (9999) <sub>BCD</sub><br>SD ← TM                                            | UPDATE<br>LSR<br>UPDATE<br>LSR  | 0: Select 1001100110011001 for loading SD<br>1: Enable load SD, 0: disable load SD<br>1: Select TM for loading SD<br>Same as above |

| DIS = TM<br>DIS = SD                                                             | DS                              | 0: Select TM for DIS<br>1: Select SD for DIS                                                                                       |

| TM < SD<br>TM ≥ SD                                                               | ALTB                            | 1: TM less than SD<br>0: TM greater than or equal to SD                                                                            |

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides

© 2008 Pearson Education, Inc.

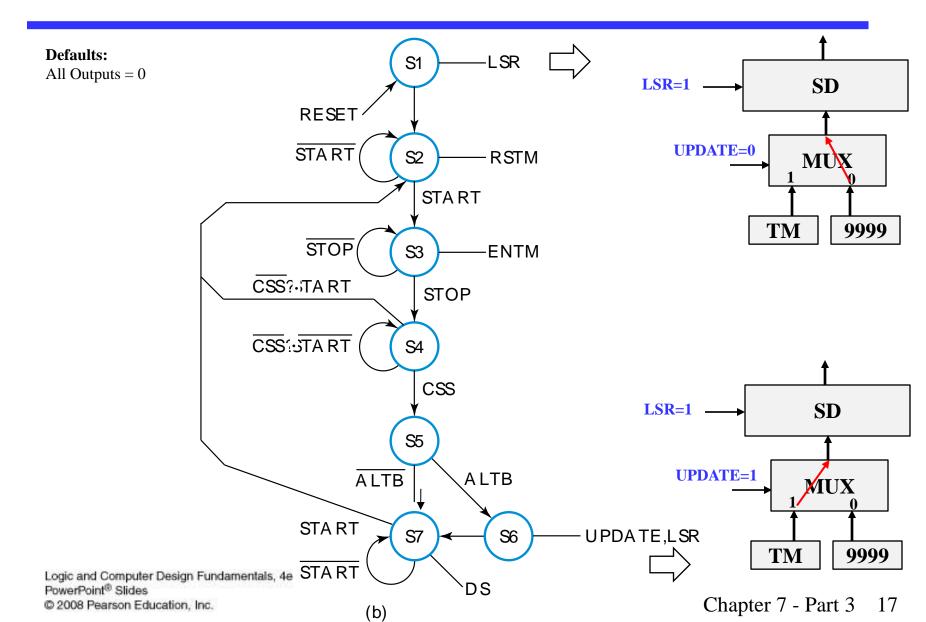

# **Example 1: DASHWATCH Determination of Internal Control/Status Signals**

#### TM – Timer RSTM TM Reset to 0000: RSTM ENTM Enable to Count Up: ENTM SD – Shortest Dash LSR **SD** • Load SD: LSR = 1; • Select input 9999: **UPDATE** = **0** UPDATE **MUX** • Select input TM: UPDATE = 1 • DIS – Display $(B_1, B_0, DP, B_{-1}, B_{-2})$ ТМ 9999 • Select input TM: DS = 0 • Select input SD: DS = 1 DS **MUX** Compare TM and SD (Status) • TM < SD: ALTB = 1**SD** TM • $TM \ge SD: ALTB = 0$

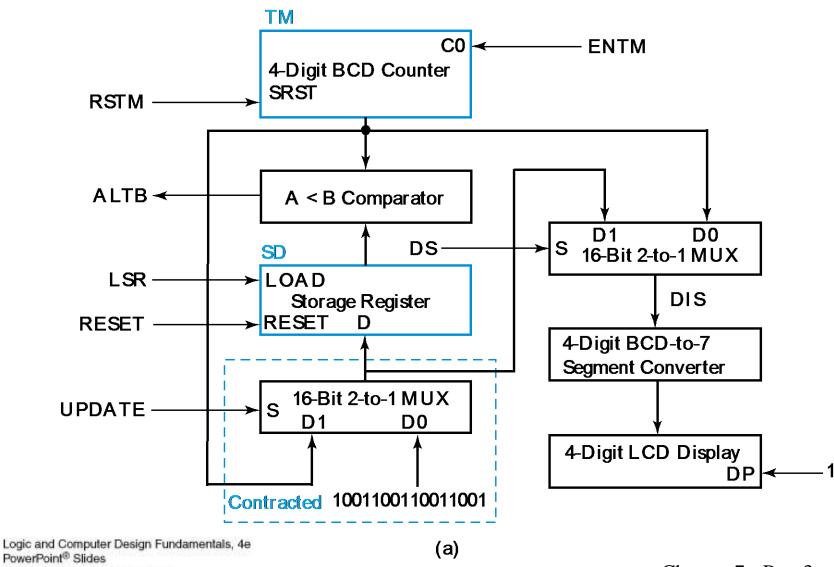

# **Example 1:DASHWATCH** Datapath

© 2008 Pearson Education, Inc.

Chapter 7 - Part 3 14

# **Example 1: DASHWATCH Datapath Development**

- TM: 4-digit BCD Counter with Synchronous Reset

- Based on previous BCD adder digit design

- synchronous reset SRST added

- $\mathbf{SRST} = \mathbf{RSTM}$

- C0 (Incoming carry) = ENTM

- A < B Comparator

- Compares TM to SD

- Designed as left-to-right iterative cell array with output C0

- SD: Standard 16-bit parallel load register

- LOAD = LSR

- Contracted standard 2-way, 16-bit multiplexer used to select between 9999<sub>BCD</sub> and TM as parallel load input D

- S = UPDATE

# **Example 1: DASHWATCH Datapath Development – Display Logic**

- 2-way 16-bit multiplexer

- Selects between TM and SD

- S = DS

- 4-digit BCD-to-7 Segment Converter

- Uses previous design

- 4-digit 7-Segment Display with Decimal Point

- 2-digit fractional part

- Decimal Point control = DP

- $\mathbf{DP} = \mathbf{1}$

## **Example 1: DASHWATCH** SMD with Control Signal Outputs Replacing Register Transfers

# **Example 1: DASHWATCH FF Input Equations**

- One-Hot State Assignment 7 bits

- State S1 entered only by using asynchronous RESET

$$D_{S1} = S1(t+1) = 0$$

$$D_{S2} = S2(t+1) = S1 + S2 \cdot \overline{START} + S4 \cdot \overline{CSS} \cdot START + S7 \cdot START$$

$$D_{S3} = S3(t+1) = S2 \cdot START + S3 \cdot \overline{STOP}$$

$$D_{S4} = S4(t+1) = S3 \cdot STOP + S4 \cdot \overline{CSS} \cdot \overline{START}$$

$$D_{S5} = S5(t+1) = S4 \cdot CSS$$

$$D_{S6} = S5 \cdot ALTB$$

$$D_{S7} = S7(t+1) = S5 \cdot \overline{ALTB} + S6 + S7 \cdot \overline{START}$$

# **Example 1: DASHWATCH Output Equations**

- LSR = S1 + S6

- RSTM = S2

- ENTM = S3

- UPDATE = S6

- DS = S7

# Handheld Game: PIG

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 5 - Part 3 20

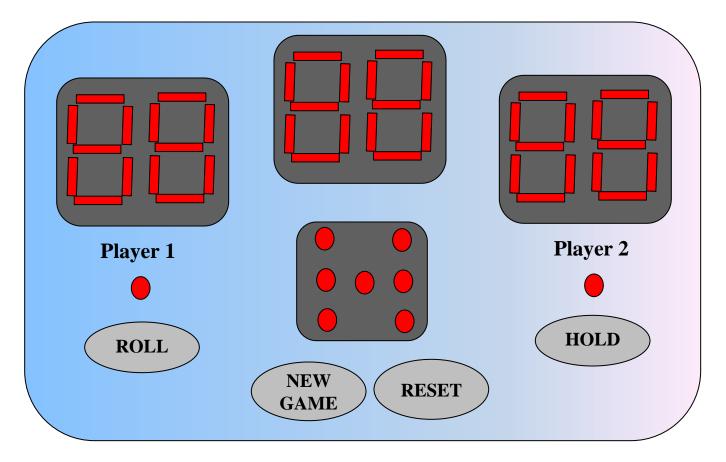

# **Example 2: PIG**

#### **Exterior View**

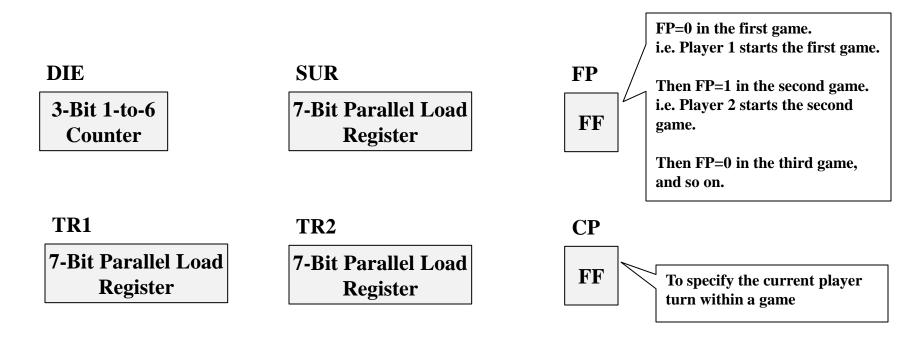

# **Example 2: PIG Registers**

**Datapath Registers**

**Control Registers**

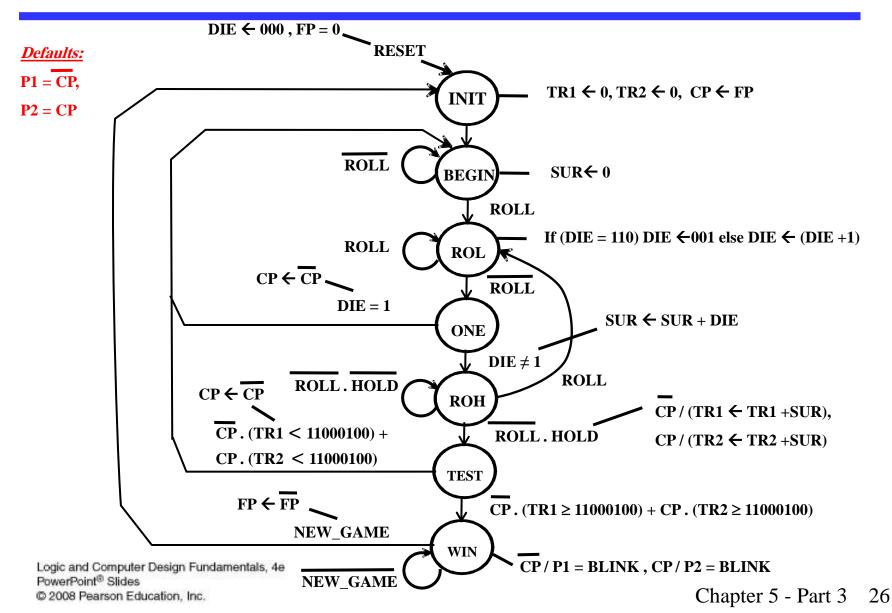

# Example 2 – PIG Specifications

- PIG is a dice game which is played with a single die that has 1 to 6 dots on its six faces.

- During each turn, the player rolls the die one or more times until either:

- 1 is rolled

- The player chooses to HOLD.

- For each roll, the value rolled, except for a 1, is added to a subtotal for the current turn.

- If a 1 is rolled, the subtotal become 0, and the player's turn is ended.

- At the end of each turn, the subtotal is added to the player's overall total, and the play passes to the other player.

- The first player to reach or exceed 100 wins.

# Example 2 – PIG Specifications

- Inputs: ROLL, HOLD, NEW\_GAME, RESET

- Outputs:

- 7-bit LED die display (DDIS)

- 7-Segment pair to display the subtotal for the current turn (SUB)

- 7-Segment pair to display the overall total for the player 1 (TP1)

- 7-Segment pair to display the overall total for the player 2 (TP2)

- Player 1 LED ON/ OFF (P1)

- Player 2 LED ON/ OFF (P2)

- Registers:

- Datapath Registers:

- 3-bit 1-to-6 Counter (DIE)

- 7-bit Parallel Load Register (SUR)

- 7-bit Parallel Load Register (TR1)

- 7-bit Parallel Load Register (TR2)

- Control Registers:

- Flip-Flop (FP)

- Flip-Flop (CP)

# **Example 2: PIG Inputs, Outputs, and Registers**

| Symbol   | Name /                                     | Туре                      |                        |

|----------|--------------------------------------------|---------------------------|------------------------|

| ROLL     | 1: Starts die rolling                      | 0: Stops die rolling      | <b>Control input</b>   |

| HOLD     | 1: Ends player turn                        | 0: Continues player turn  | <b>Control input</b>   |

| NEW_GAME | 1: Stats new game                          | 0: Continues current game | Control input          |

| RESET    | 1: Reset game to INIT state                | 0: No action              | <b>Control input</b>   |

| DDIS     | 7-bit LED die display array                | Data output vector        |                        |

| SUB      | 14-bit 7-segment pair (a, b, c, d, e, f, g | Data output vector        |                        |

| TP1      | 14-bit 7-segment pair (a, b, c, d, e, f, g | Data output vector        |                        |

| TP2      | 14-bit 7-segment pair (a, b, c, d, e, f, g | Data output vector        |                        |

| P1       | 1: Player 1 LED on                         | 0: Player 1 LED off       | Data output            |

| P2       | 1: Player 2 LED on                         | 0: Player 2 LED off       | Data output            |

| DIE      | Die value- Specialized counter to cour     | 3- bit data register      |                        |

| SUR      | Subtotal for active player: parallel log   | 7- bit data register      |                        |

| TR1      | Overall total for player 1: parallel loa   | 7- bit data register      |                        |

| TR2      | Overall total for player 2: parallel loa   | 7- bit data register      |                        |

| FP       | First player – flip-flop 0: Playe          | r 1, 1: Player 2          | 1-bit control register |

| СР       | Current player – flip-flop 0: Playe        | r 1, 1: Player 2          | 1-bit control register |

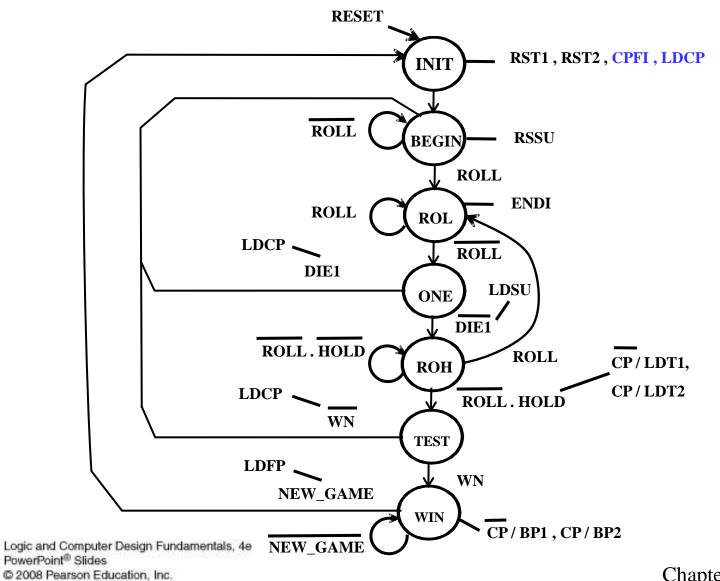

# Example 2: PIG SMD with Register Transfer Outputs

# Example 2: PIG Output Control/Status Table

| Action or Status                                                                                    | Control or Status<br>Signals | Meaning for                                                                                                                        | values 1 and 0               |

|-----------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| $TR1 \leftarrow 0$<br>TR1 \leftarrow TR1 + SUR                                                      | RST1<br>LDT1                 | 1: Reset TR1 (Synchronous reset),<br>1: Add SUR to TR1,                                                                            | 0: No action<br>0: No action |

| $TR2 \leftarrow 0$<br>TR2 $\leftarrow$ TR2 + SUR                                                    | RST2<br>LDT2                 | 1: Reset TR2 (Synchronous reset),<br>1: Add SUR to TR2,                                                                            | 0: No action<br>0: No action |

| SUR ← 0<br>SUR ← SUR+ DIE                                                                           | RSSU<br>LDSU                 | 1: Reset SUR (Synchronous reset),<br>1: Add DIE to SUR,                                                                            | 0: No action<br>0: No action |

| DIE ← 000<br>if (DIE = 110) DIE ←001 else DIE ← (DIE +1)                                            | RESET<br>ENDI                | 1: Reset DIE to 000 (Asynchronous<br>1: Enable DIE to increment,                                                                   | reset)<br>0: Hold DIE value  |

| P1 = BLINK                                                                                          | BP1                          | 1: Connect P1 to BLINK,                                                                                                            | 0: Connect P1 to 1           |

| P2 = BLINK                                                                                          | BP2                          | 1: Connect P2 to BLINK,                                                                                                            | 0: Connect P2 to 1           |

| $CP \leftarrow FP$ $CP \leftarrow \overline{CP}$                                                    | CPFI<br>LDCP<br>CPFI<br>LDCP | 1: Select FP for CP<br>1: Load <u>CP,</u><br>0: Select CP for CP<br>1: Load CP,                                                    | 0: No action<br>0: No action |

| $\begin{array}{l} \text{FP} \leftarrow \underline{0} \\ \text{FP} \leftarrow \text{FP} \end{array}$ | RESET<br>LDFP                | Asynchronous reset<br>1: Invert FP,                                                                                                | 0: Hold FP                   |

| DIE = 1<br>$DIE \neq 1$                                                                             | DIE1                         | 1: DIE equal to 1<br>0: DIE not equal to 1                                                                                         |                              |

| TR1 ≥ 11000100                                                                                      | CP<br>WN                     | 0: Select TR1 for ≥ 11000100<br>1: The Selected TR <sub>i</sub> ≥ 11000100<br>0: The Selected TR <sub>i</sub> < 11000100           |                              |

| TR2 ≥ 11000100                                                                                      | CP<br>WN                     | 1: Select TR2 for $\geq$ 11000100<br>1: The Selected TR <sub>i</sub> $\geq$ 11000100<br>0: The Selected TR <sub>i</sub> < 11000100 |                              |

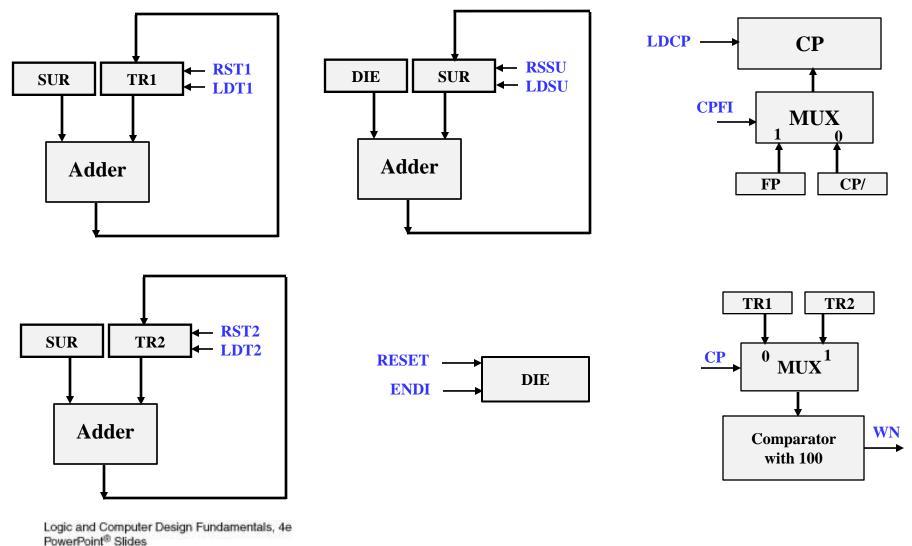

# **Example 2: PIG Datapath and Control Registers**

© 2008 Pearson Education, Inc.

Chapter 7 - Part 3 28

## **Example 2: PIG** SMD with Control Signal Outputs Replacing Register Transfers

Chapter 5 - Part 3 29

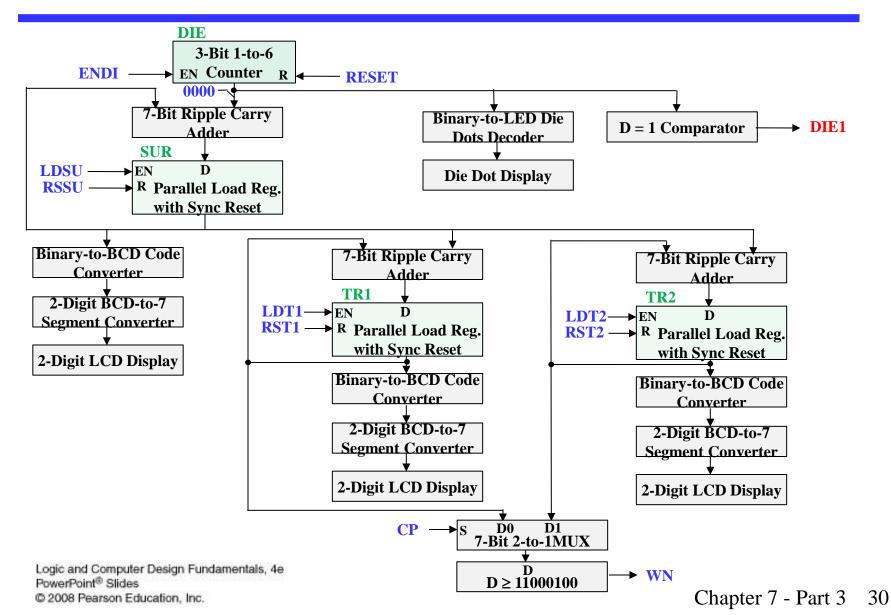

# **Example 2: PIG Datapath and Control Registers**

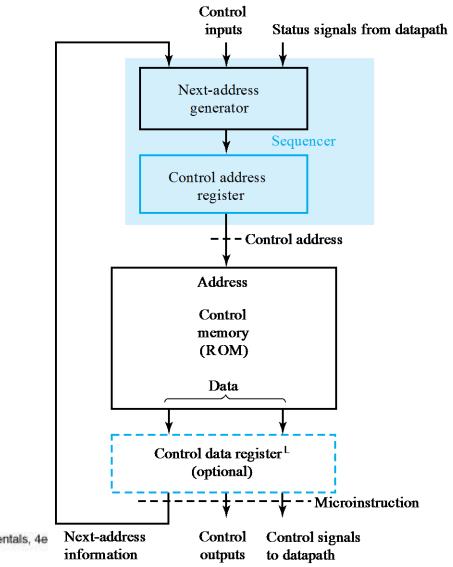

# **Microprogrammed Control**

- Microprogrammed Control a control unit with binary control values stored as <u>words</u> in <u>memory</u>.

- Microinstructions words in the control memory.

- Microprogram a sequence of microinstructions.

- Control Memory RAM or ROM memory holding the microinstructions.

- Writeable Control Memory RAM Memory into which microinstructions may be written

# Microprogrammed Control (continued)

Chapter 7 - Part 3 32

# **Terms of Use**

- All (or portions) of this material © 2008 by Pearson Education, Inc.

- Permission is given to incorporate this material or adaptations thereof into classroom presentations and handouts to instructors in courses adopting the latest edition of Logic and Computer Design Fundamentals as the course textbook.

- These materials or adaptations thereof are not to be sold or otherwise offered for consideration.

- This Terms of Use slide or page is to be included within the original materials or any adaptations thereof.