#### BROADBAND AND HIGH SPEED NETWORKS

### **II - MULTISTAGE SWITCH**

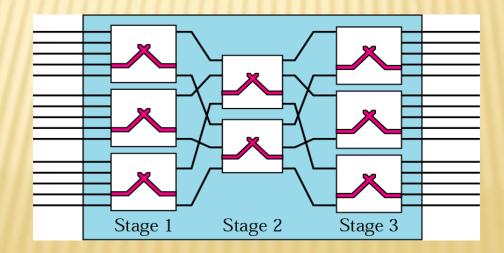

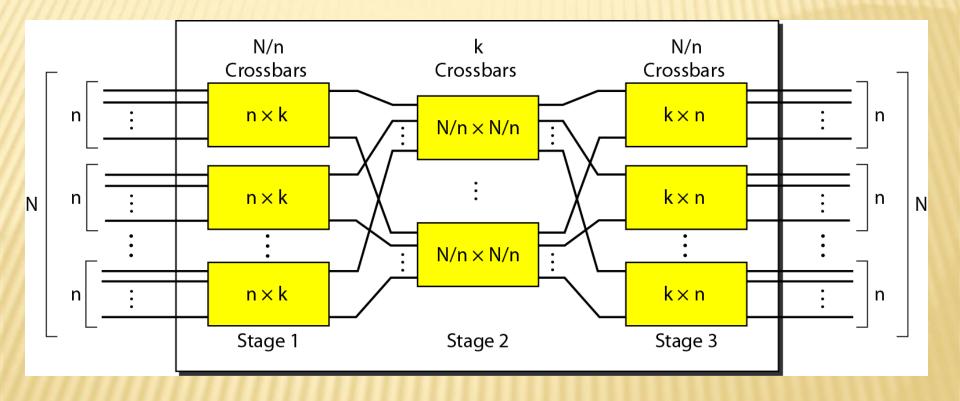

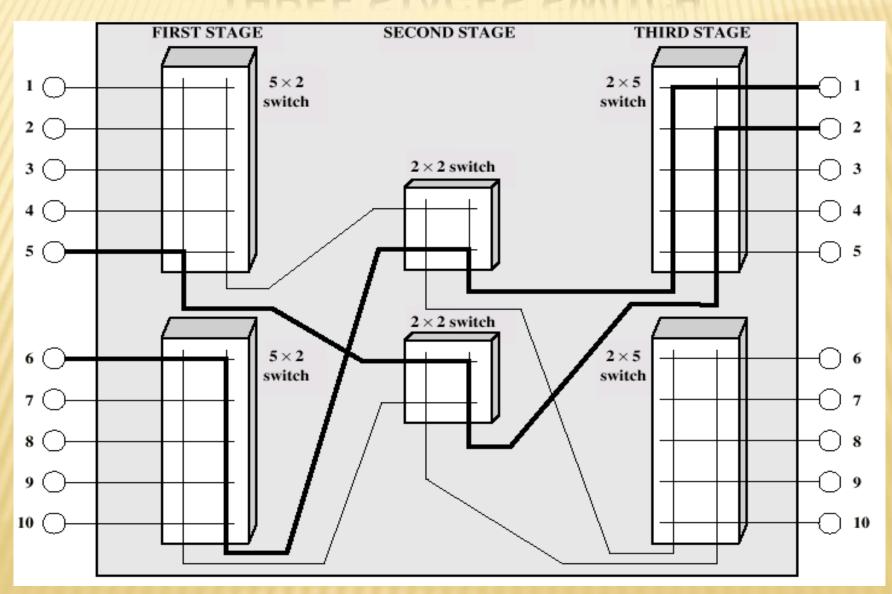

- Multistage switch combines crossbar switches in several stages.

- Design of a multistage switch depends on the number of stages and the number of switches required (or desired) in each stage.

- Normally, the middle stages have fewer switches than do the first and last stages.

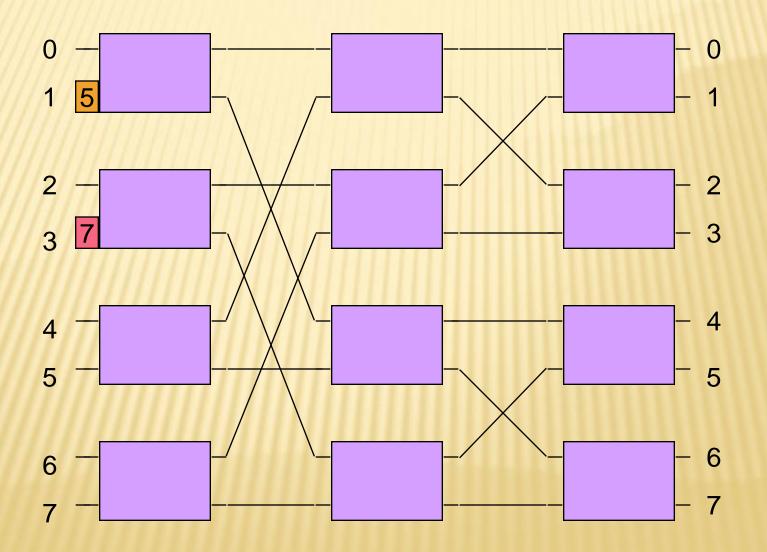

#### Multistage switch

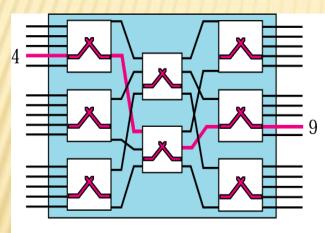

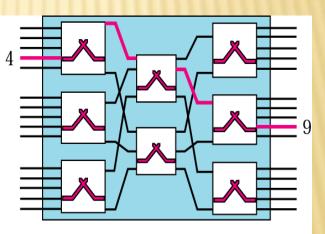

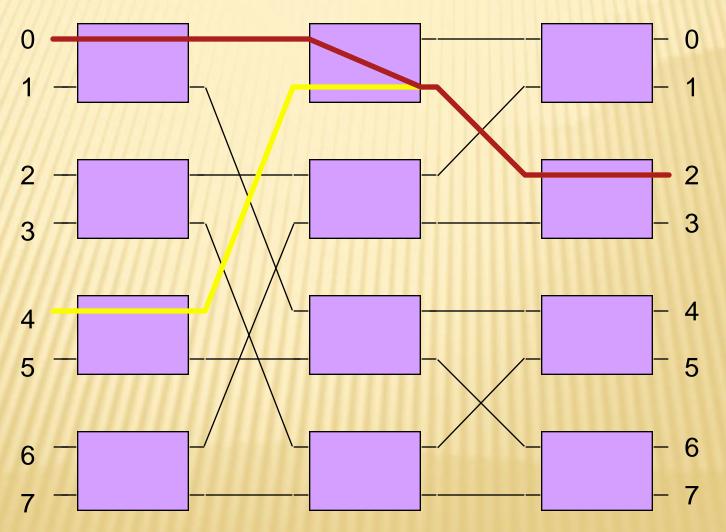

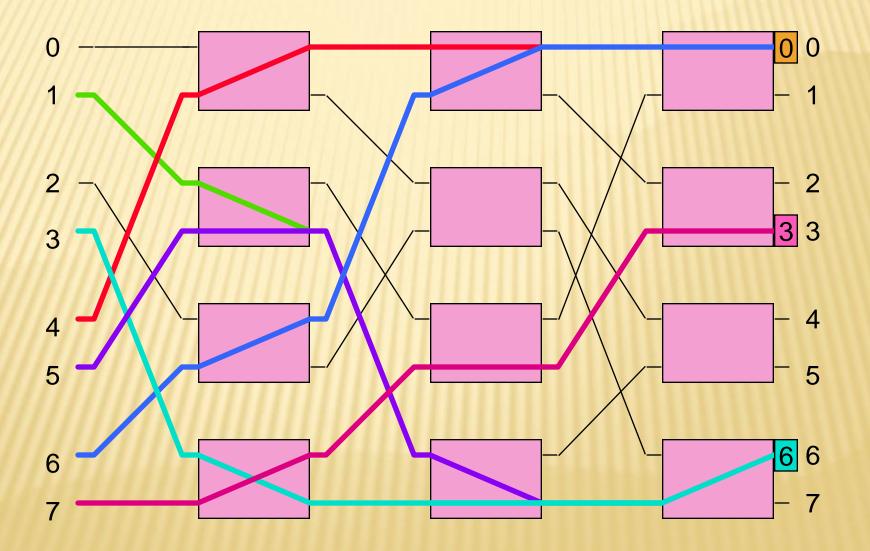

### **MULTIPLE SWITCHING PATHS**

- Multiple paths are available in multistage switches.

- Blocking refers to times when two inputs are looking for the same output. The output port is blocked.

a. First option

b. Second option

### **THREE STAGES SWITCH**

# **CIRCUIT SWITCH CONCEPTS & ELEMENTS**

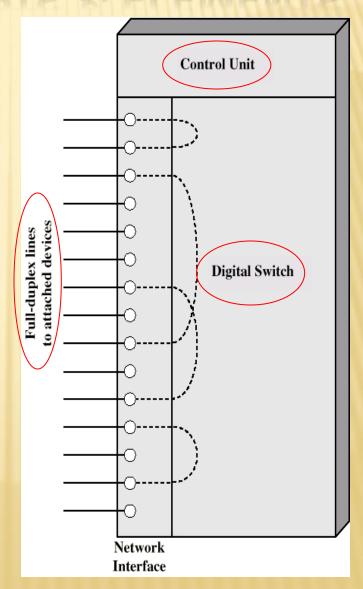

#### Digital Switch

- Provide transparent signal path between devices

- Network Interface

- Control Unit

- Establish connections

- Generally on demand

- Handle and acknowledge requests

- Determine if destination is free

- construct path

- Maintain connection

- > Disconnect

#### **DIGITAL SWITCH: BLOCKING VS. NON-BLOCKING**

#### Blocking

- A network is unable to connect end stations because all paths are in use

- > Used on voice systems

- Short duration calls

#### **Non-blocking**

- > Permits all stations to connect (in pairs) at once

- > Used for some data connections

#### II. Multistage Interconnection Networks (MINs):

#### **Characteristics:**

#### 1. Full Access:

- Every input link can reach to any output link in a single pass.

- In MINs, by using 2×2 switching elements, only log<sub>2</sub>N stages are required to achieve full access capability.

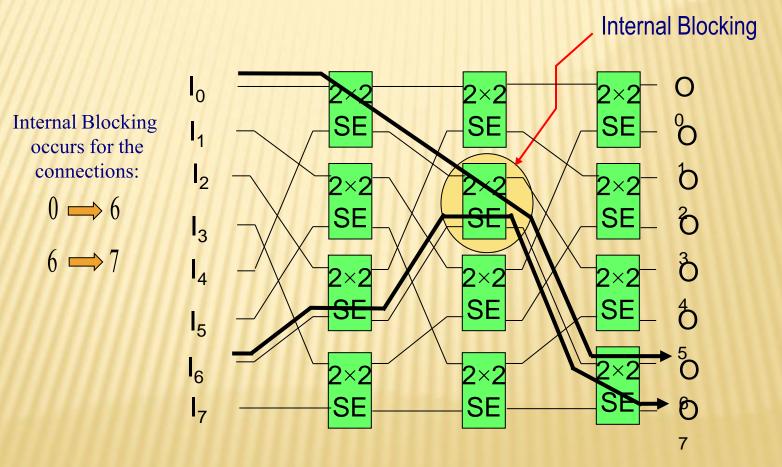

#### 2. Strictly Non-Blocking vs. Internal Blocking:

- Strictly non-blocking Switch can realize N! permutations without any rearrangement of the existing connections.

- MINs with fewer stages suffer problem of internal blocking.

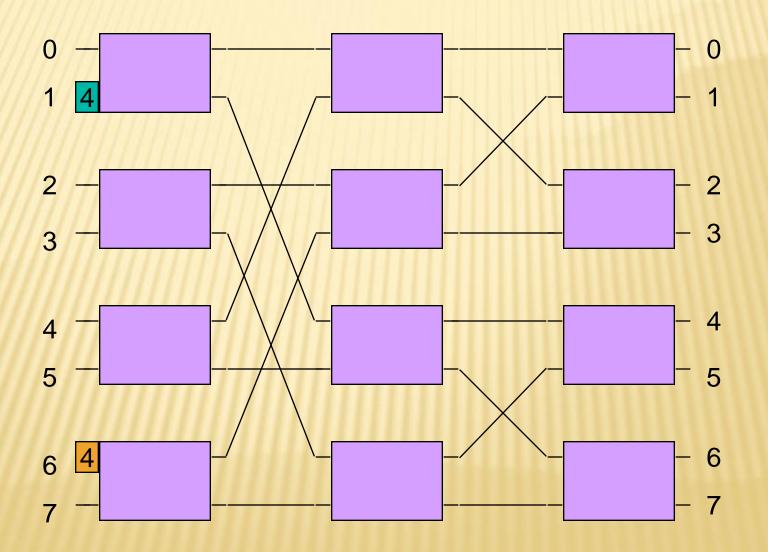

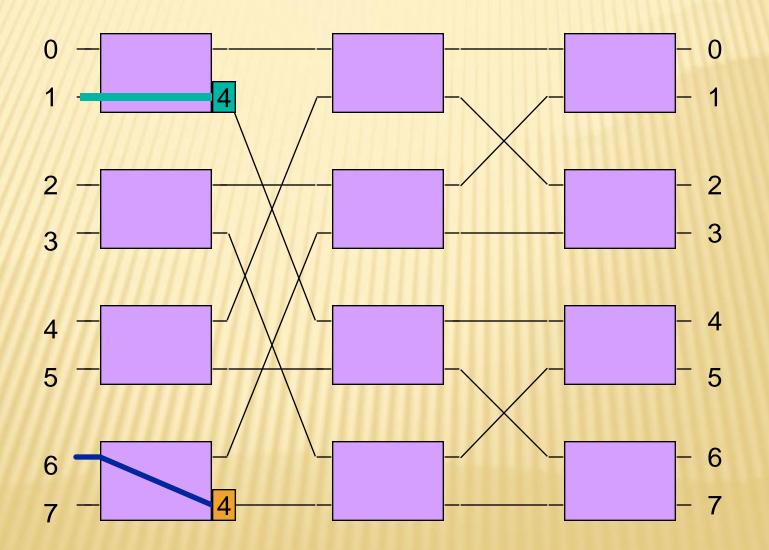

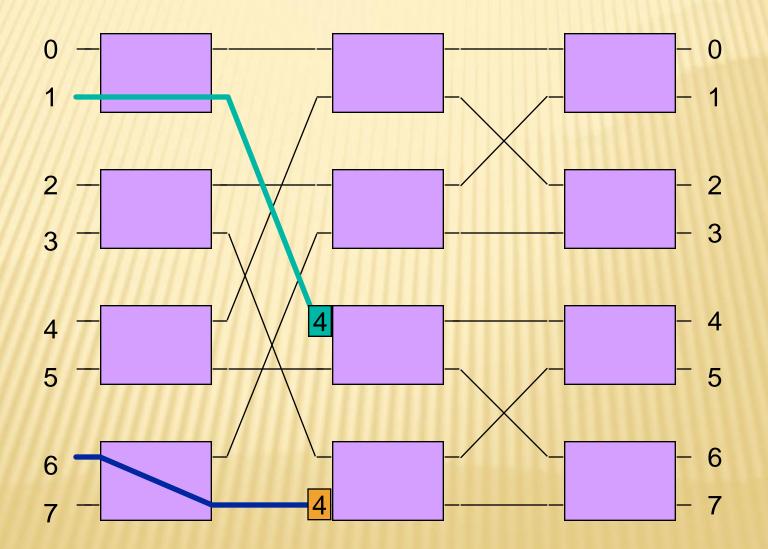

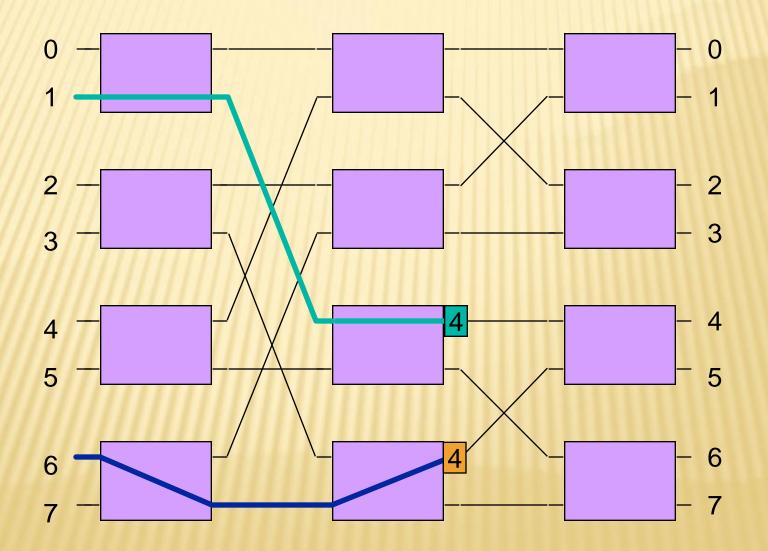

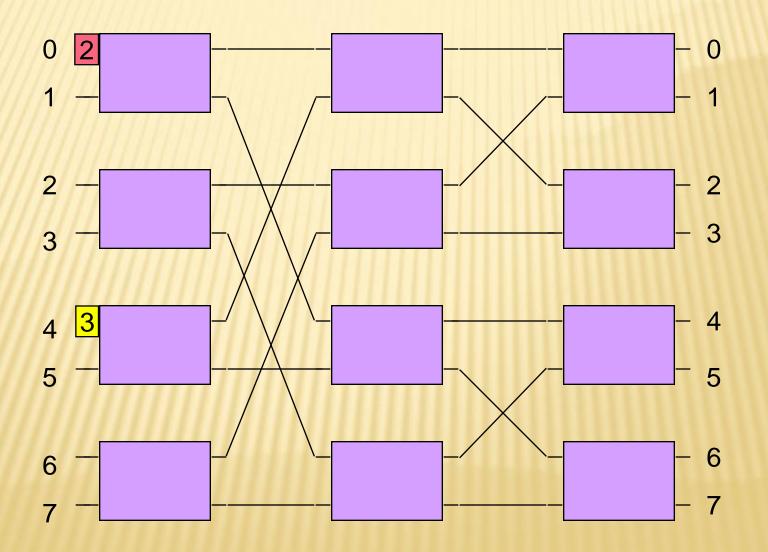

### **INTERNAL BLOCKING IN (MIN)**

#### **3. Rearrangeable Networks:**

- MINs are capable to realize N! permutations by choosing the appropriate connections.

- This type of MINs requires a large number of stages  $(3\log_2 N 4)$ .

#### 4. Combinatorial Power:

- It is the ratio of the number of permutations realizable by the MINs to the total number of possible permutations (N!).

- ✤ A MIN has log₂N stages are required to achieve full access capability, and in each stage, there are N/2 of 2×2 switching elements.

- Since each switching element has two configurations, namely straight and exchange, therefore, number of permutations realizable by the MINs is 2<sup>N/2\*log</sup><sup>N</sup>.

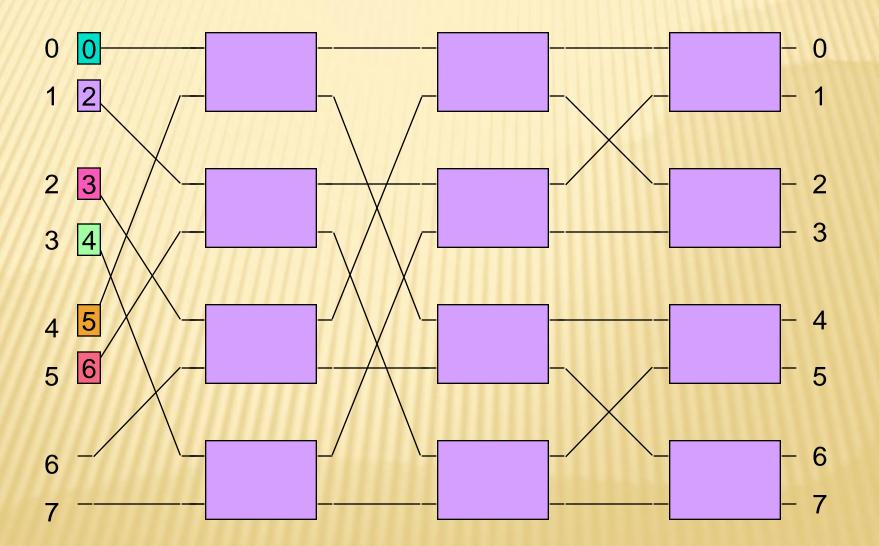

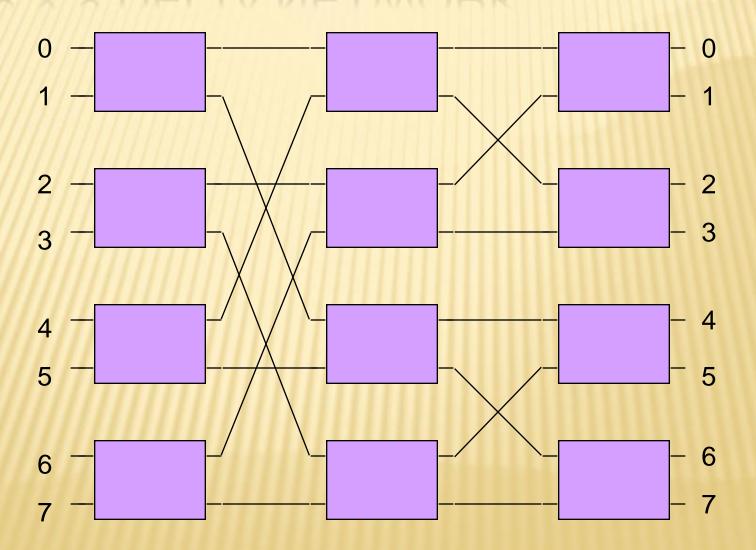

# **DELTA NETWORK**

- The <u>delta network</u> is one example of a multistage interconnection network (Banyan Network) that can be used as a switch fabric.

- In banyan networks, there is a single path from each input port to each output port.

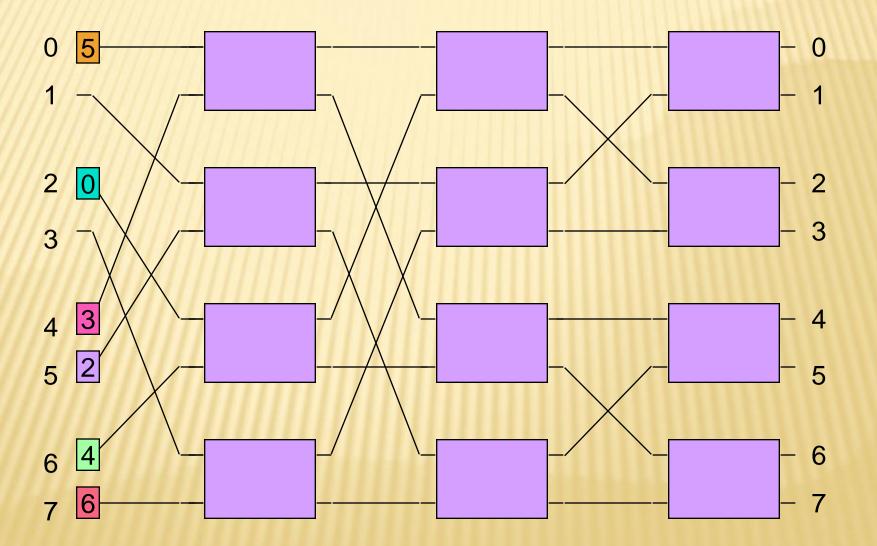

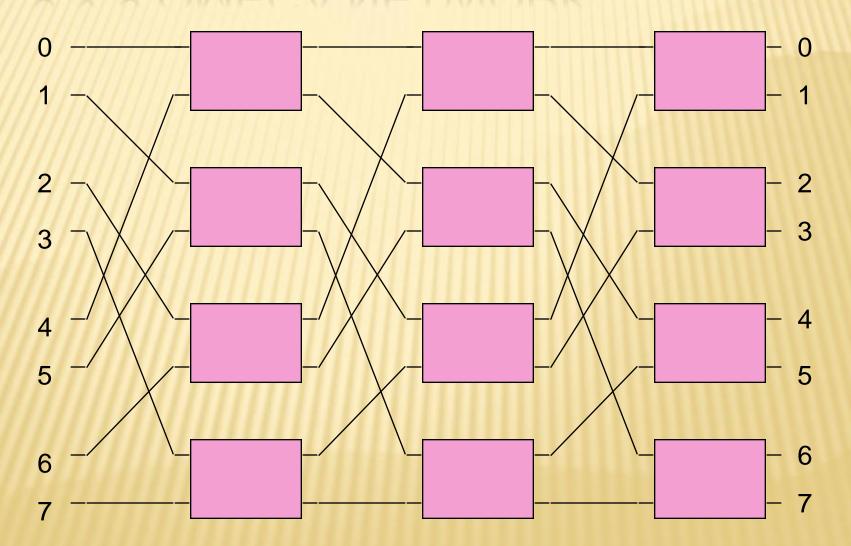

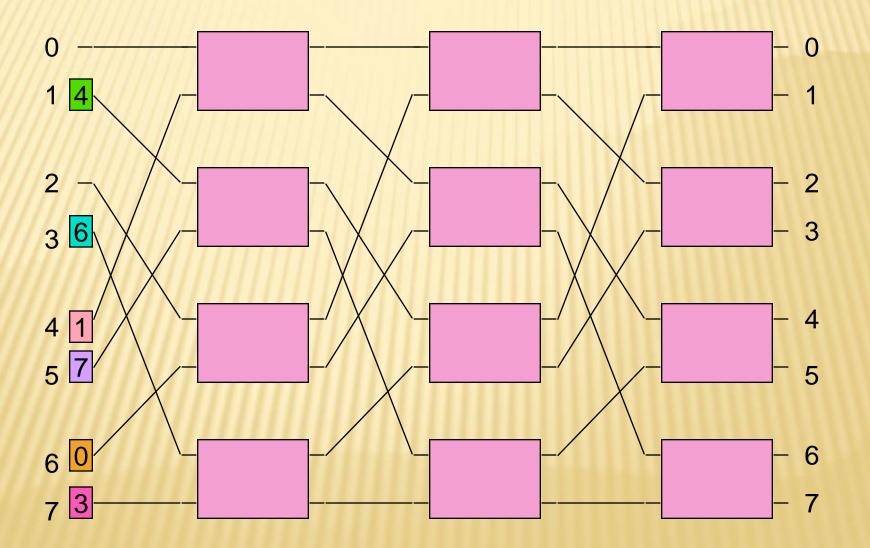

#### 8 X 8 DELTA NETWORK

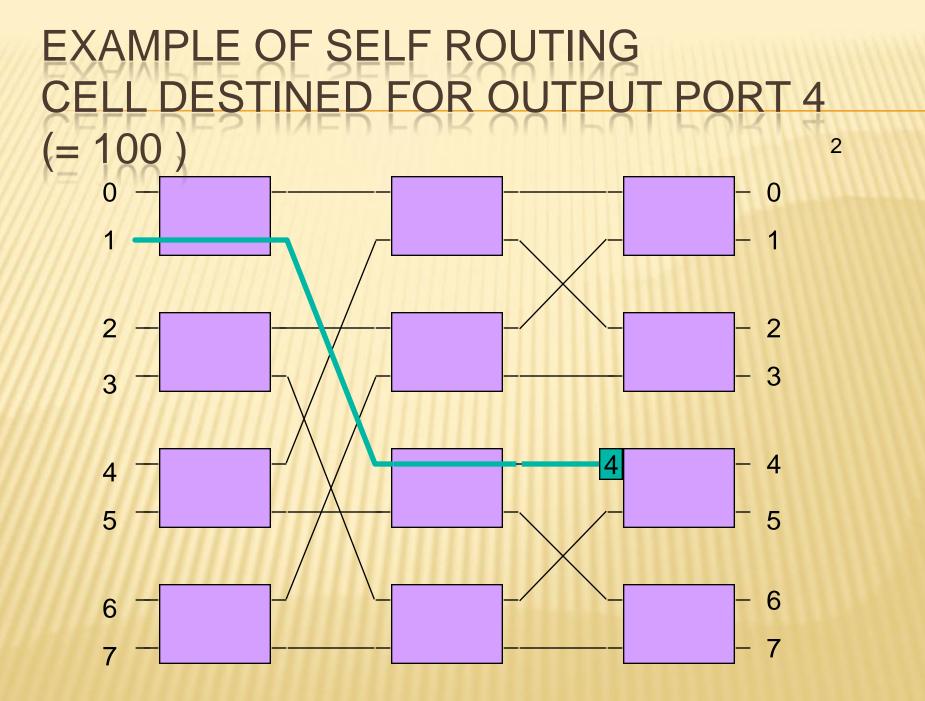

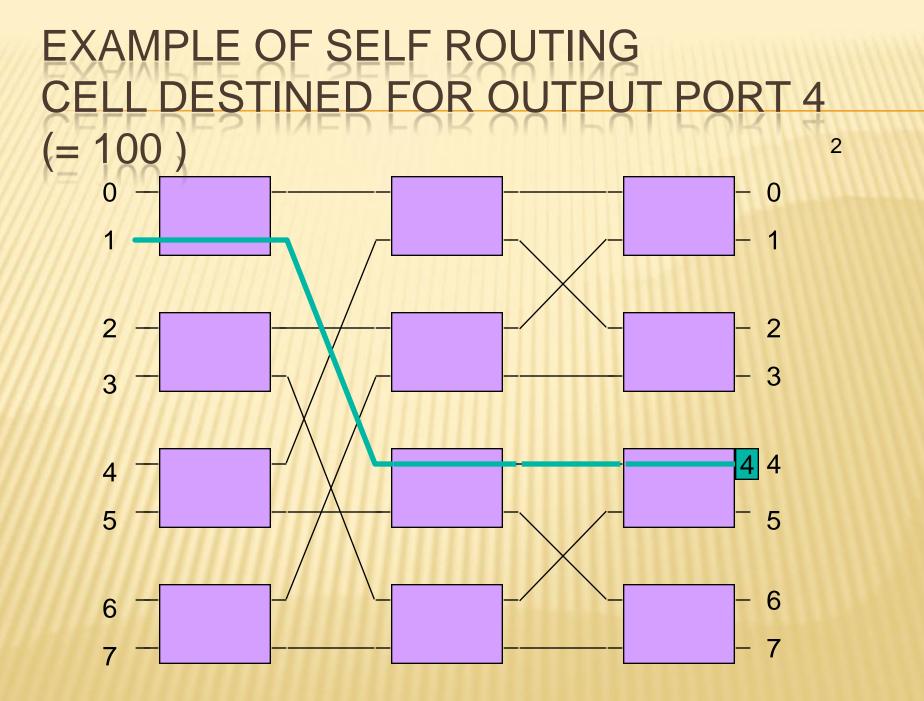

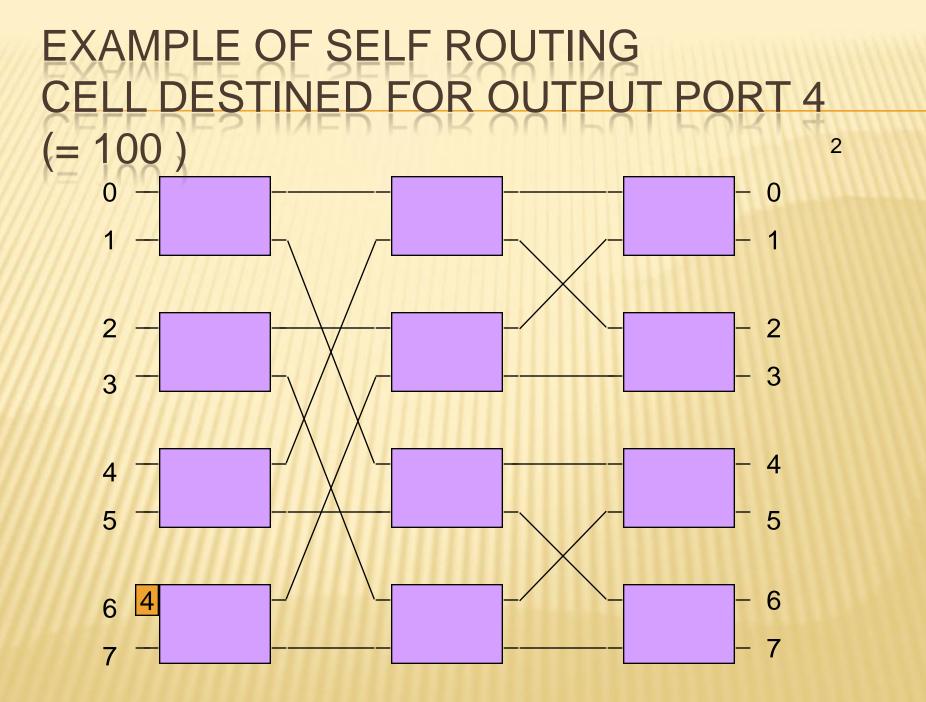

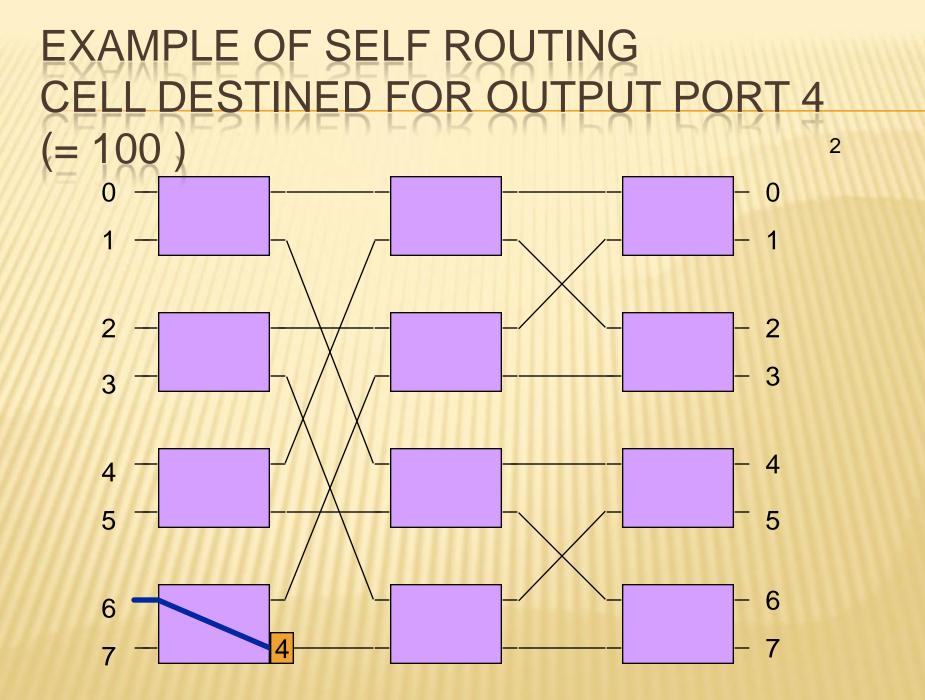

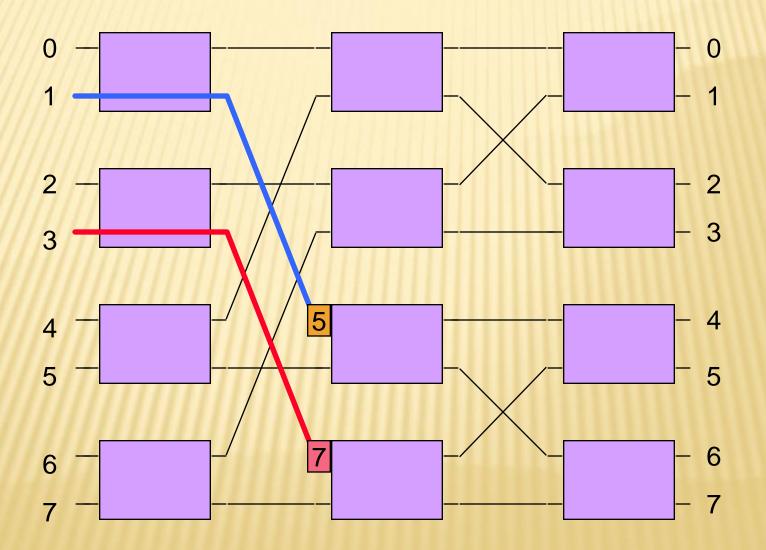

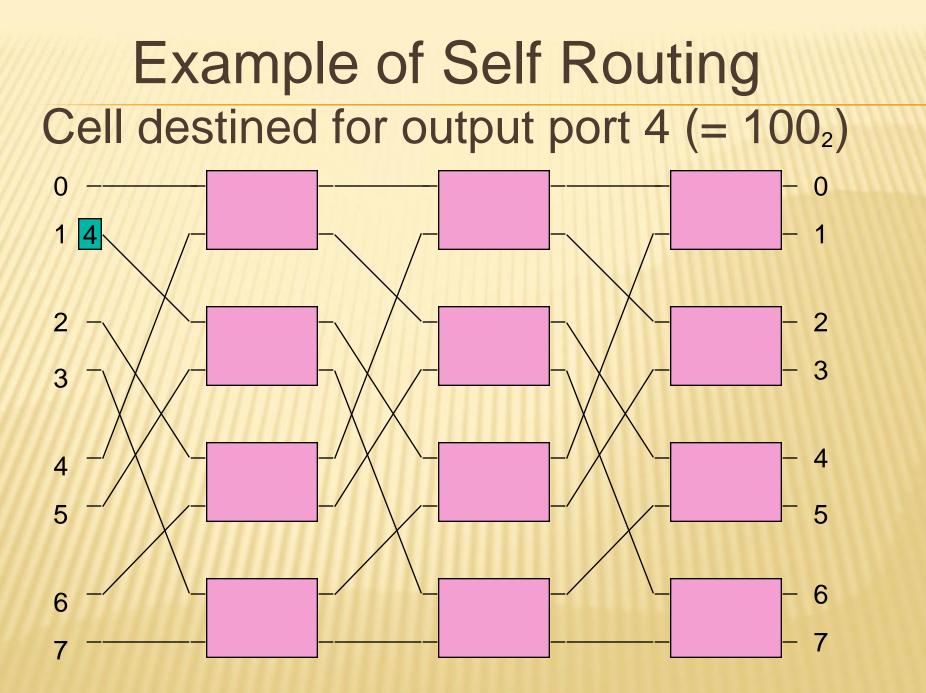

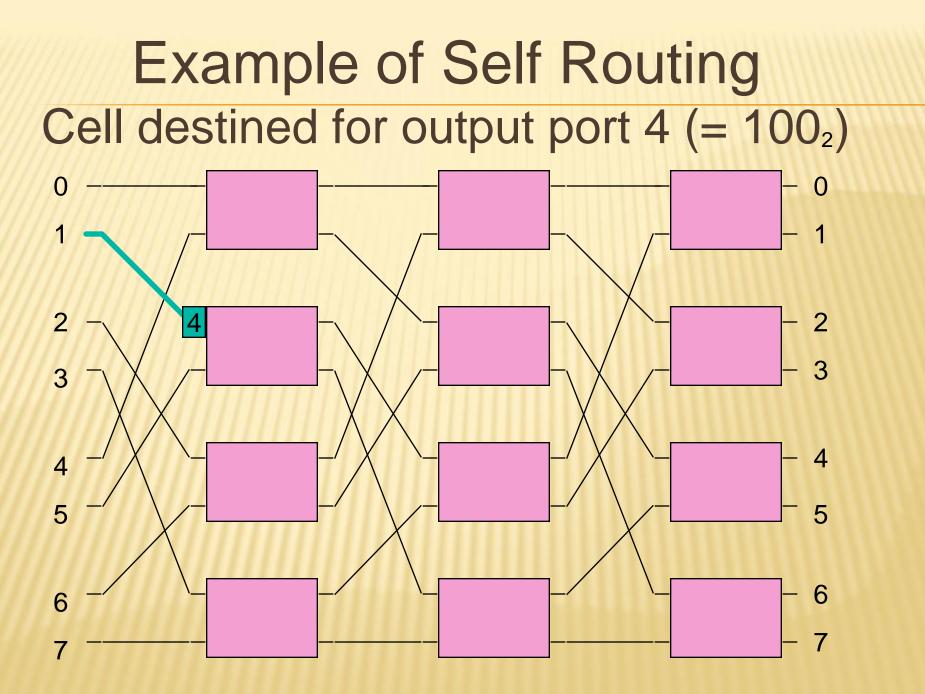

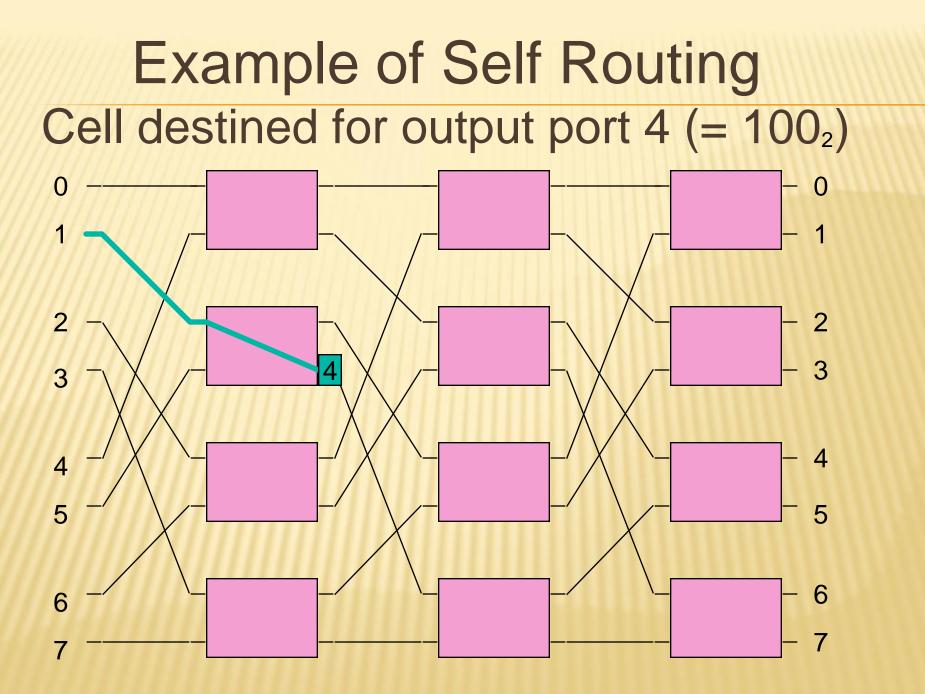

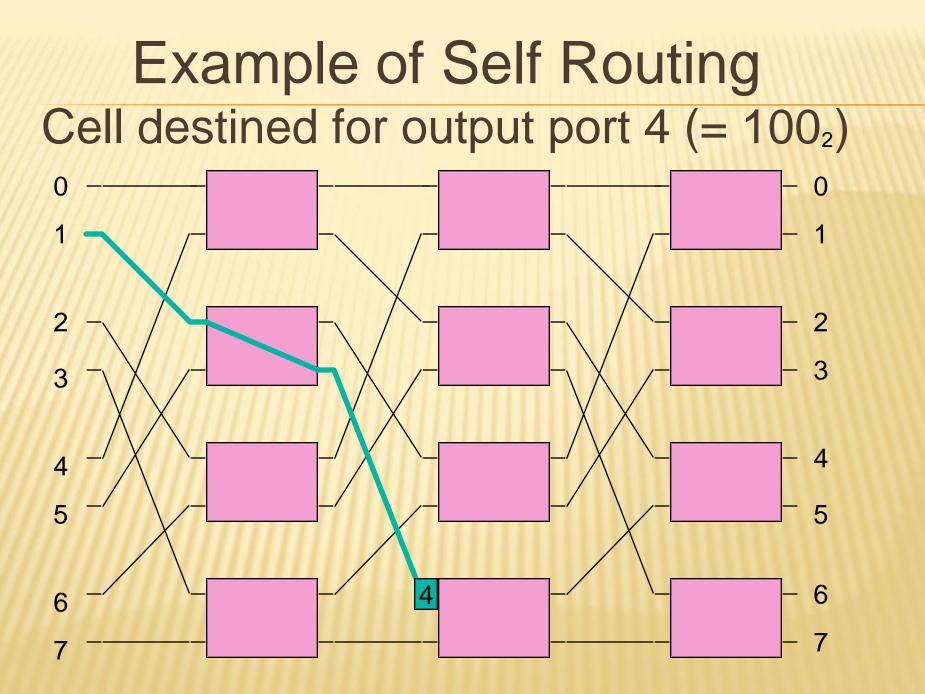

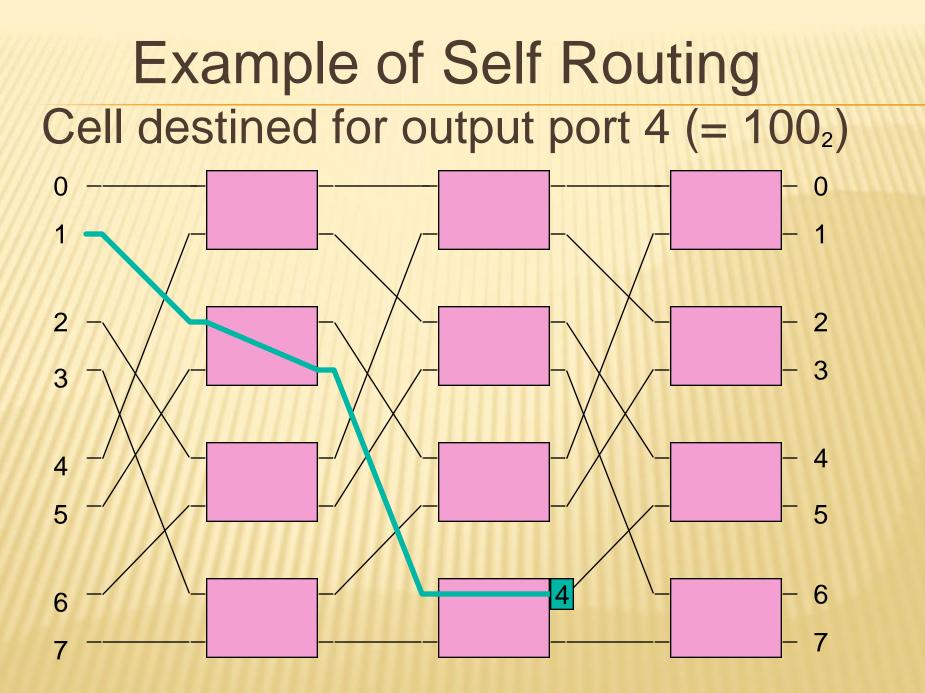

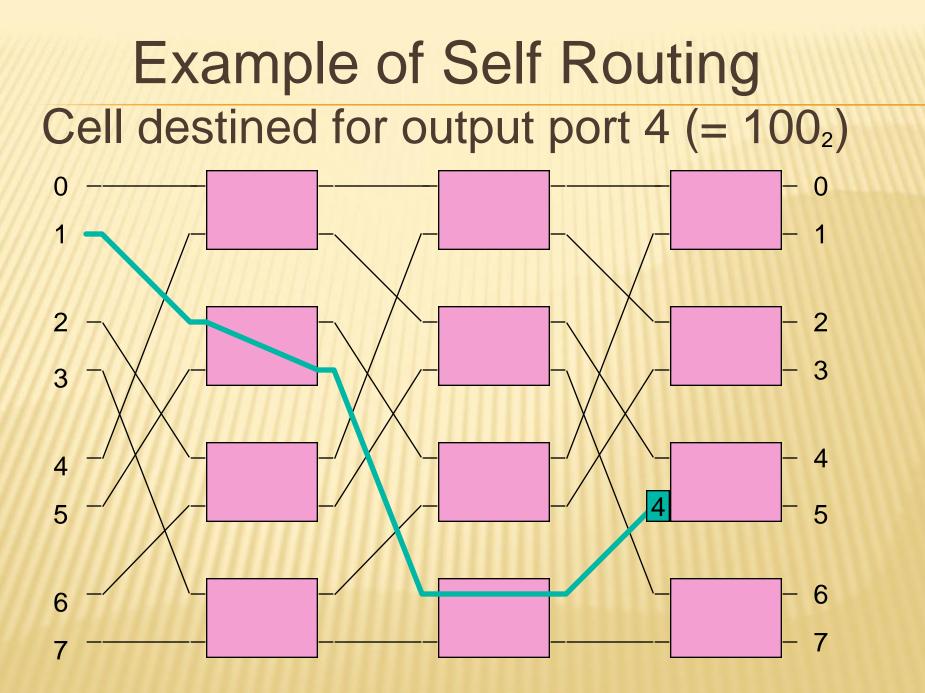

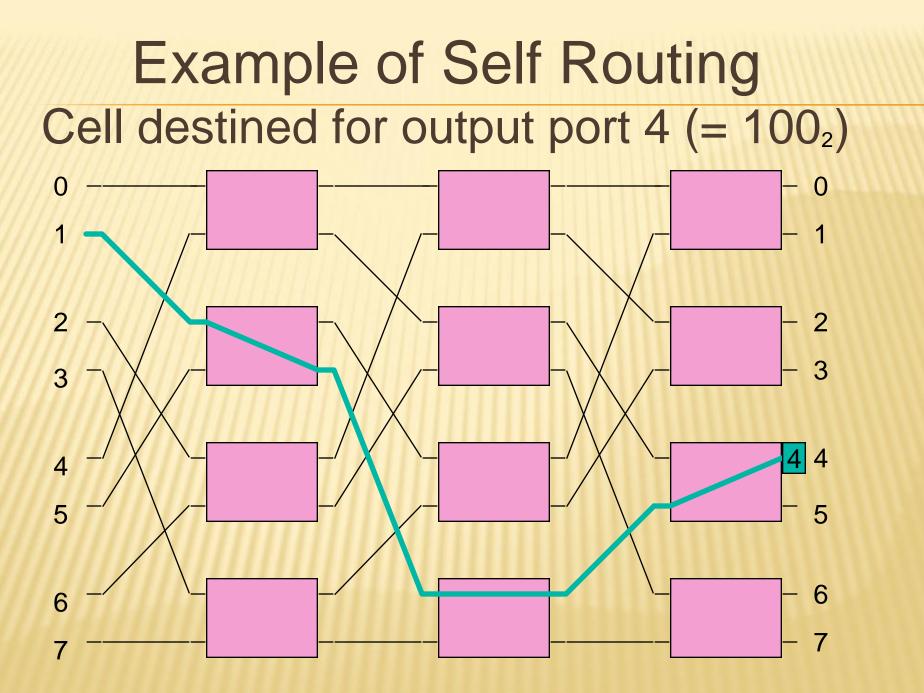

# SELF ROUTING

- Delta network has <u>self-routing property</u>

- The path for a cell to reach its destination can be determined directly from its <u>routing tag (i.e.,</u> destination port id)

- Stage k of the MIN looks at bit k of the tag

- If <u>bit k is 0</u>, then send cell out <u>upper port</u>

- If <u>bit k is 1</u>, then send cell out <u>lower port</u>

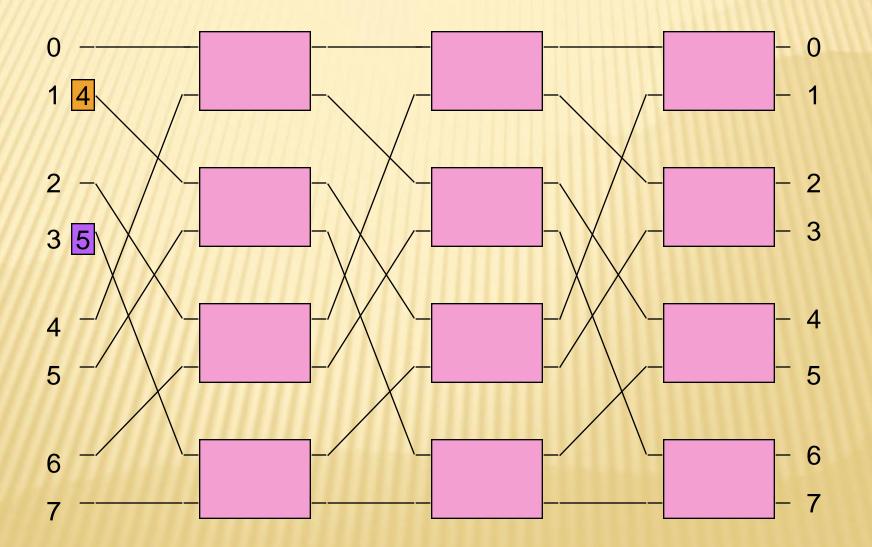

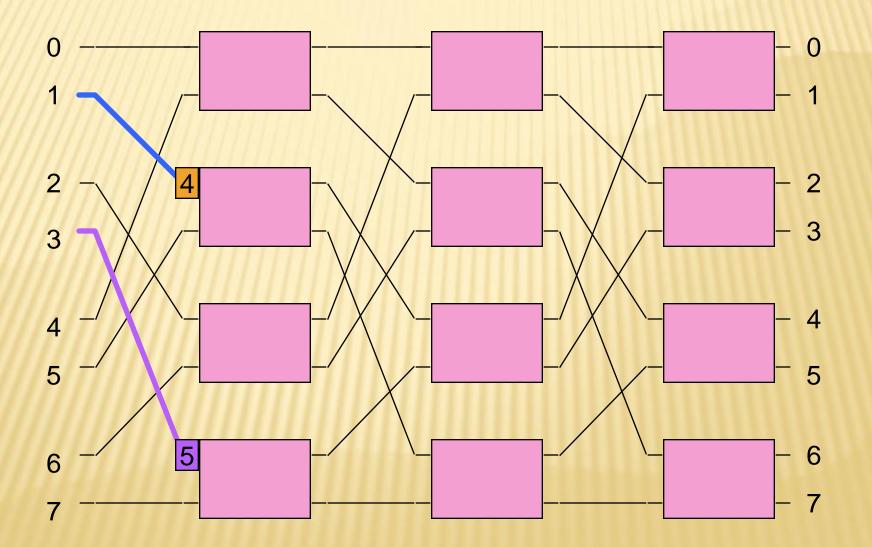

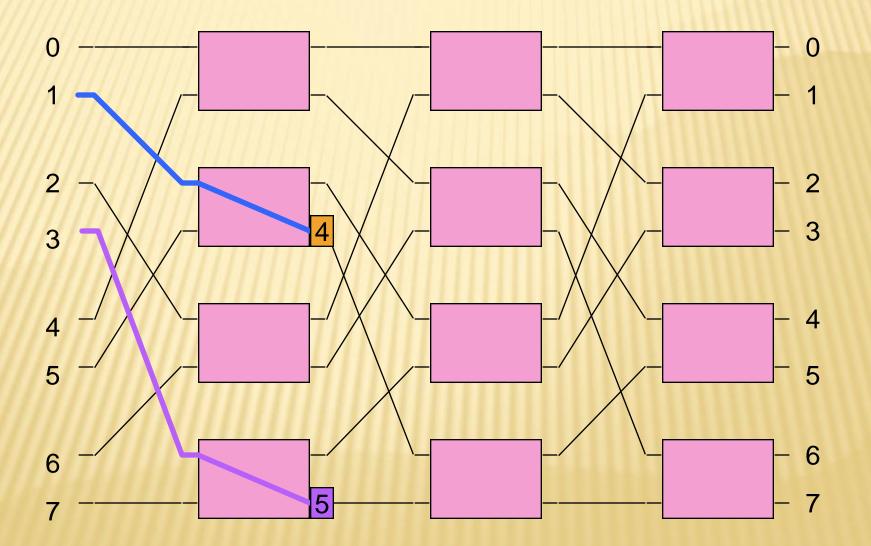

## **MULTIPLE CONCURRENT PATHS**

- > Up to now, all examples have worked wonderfully because each incoming cell was destined to a different output port

- What happens if more than one cell destined to same output port?

- Answer: <u>output port contention</u>

- Result: <u>cell loss</u> in a bufferless network

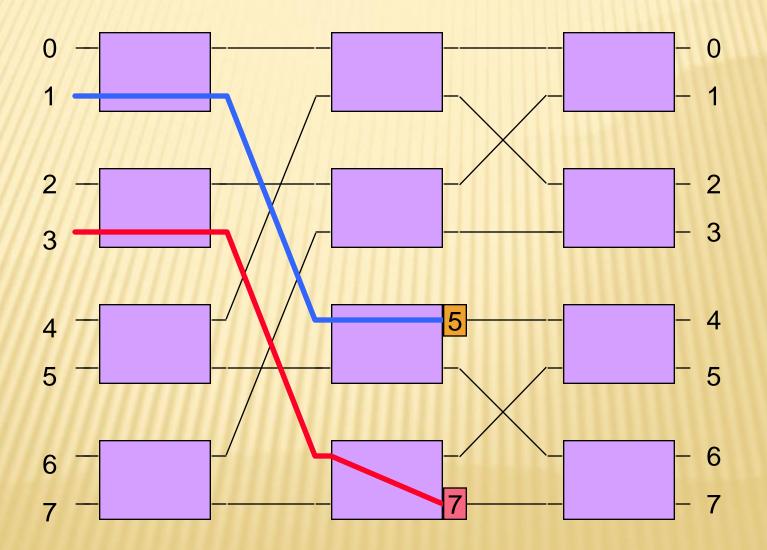

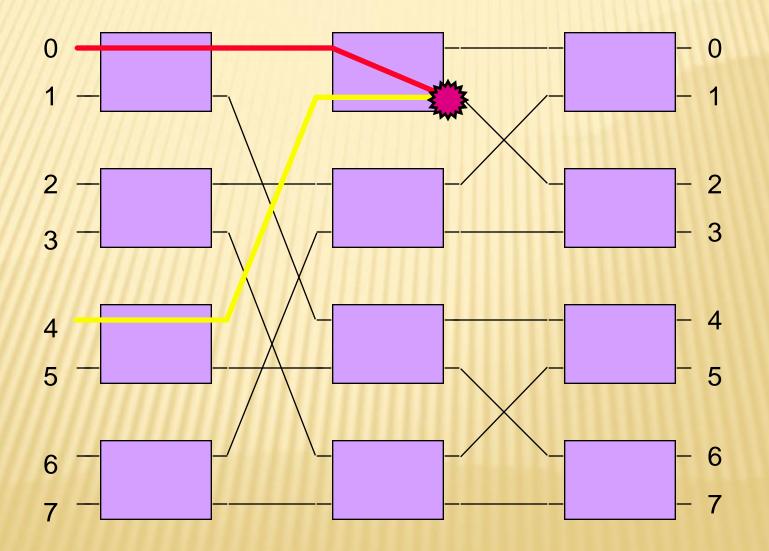

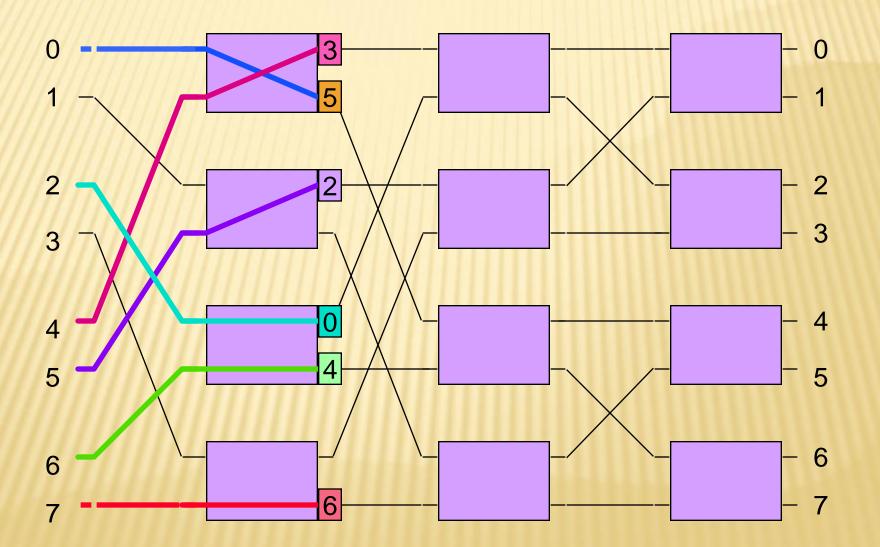

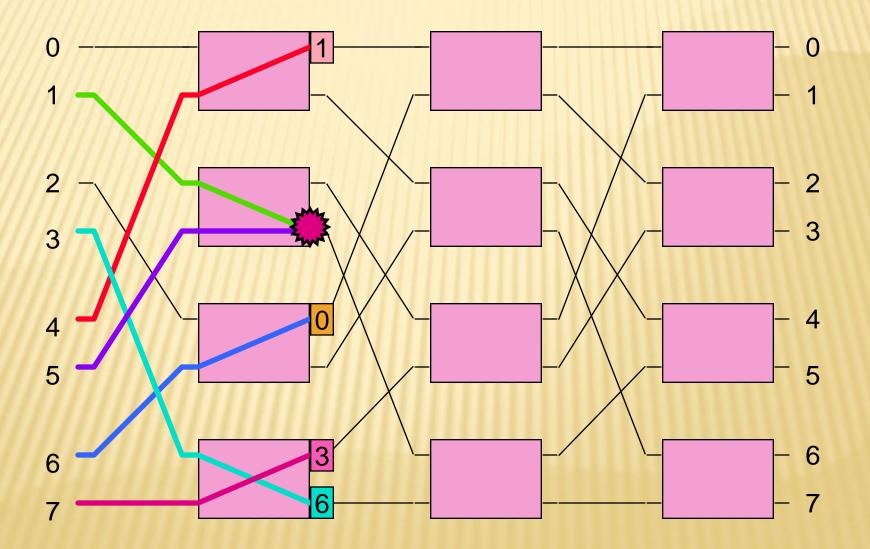

- It is also possible for two incoming cells that are destined to <u>different output ports</u> to require the <u>same internal link</u> in the switch

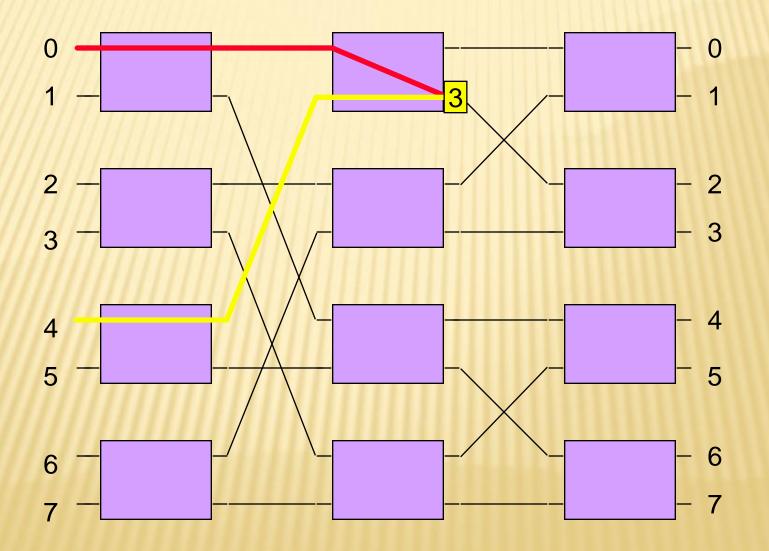

- × Called path contention or internal blocking

- \* Again, the result in a bufferless switch fabric is <u>cell loss</u> (one cell wins, one loses)

- Path contention and output port contention <u>can seriously degrade the achievable</u> <u>throughput of the switch</u>

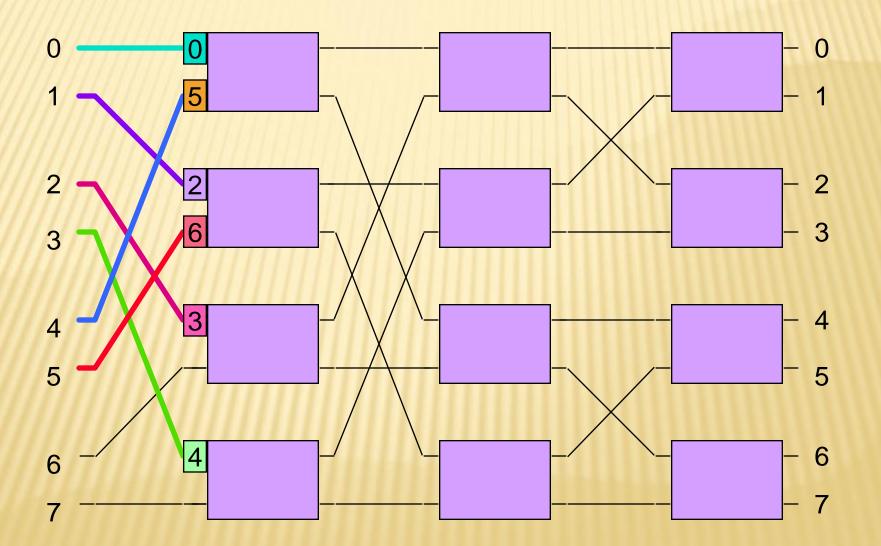

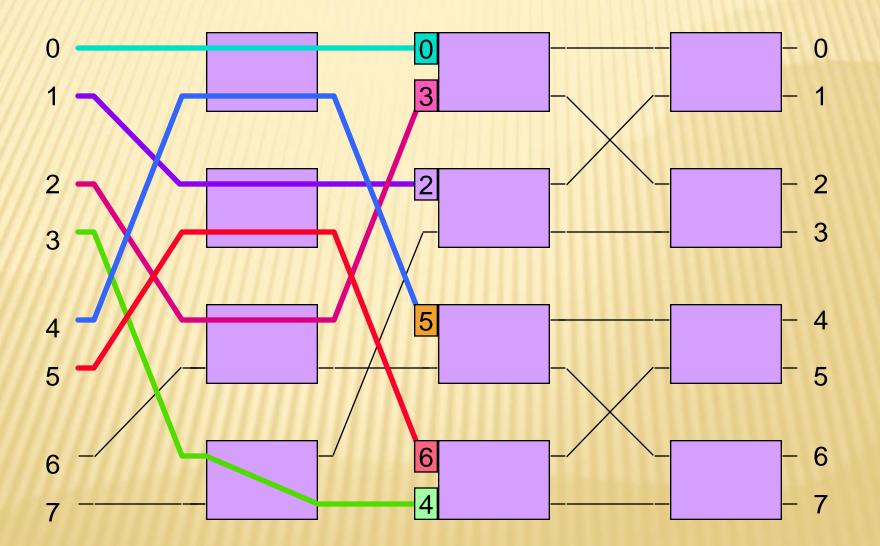

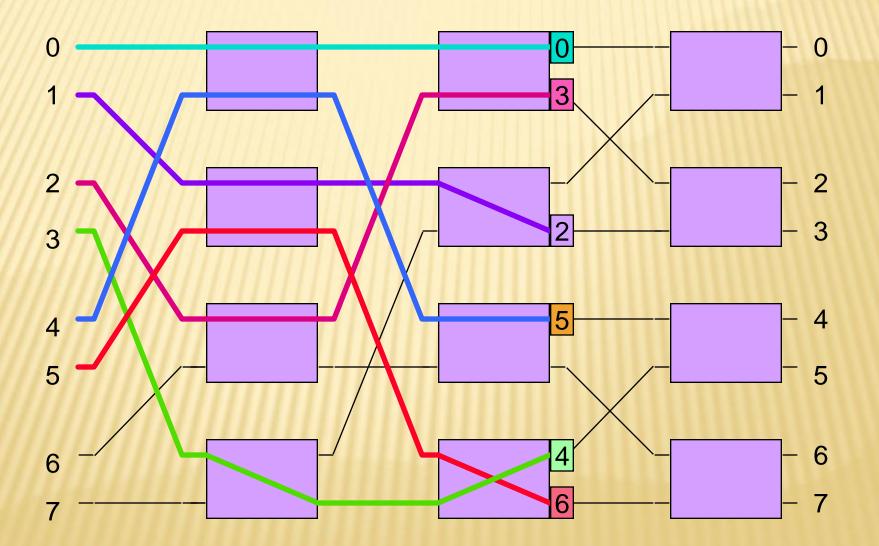

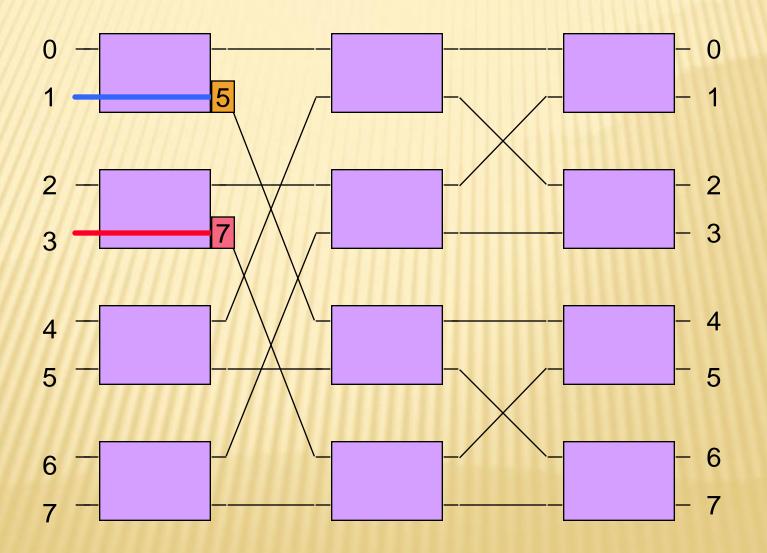

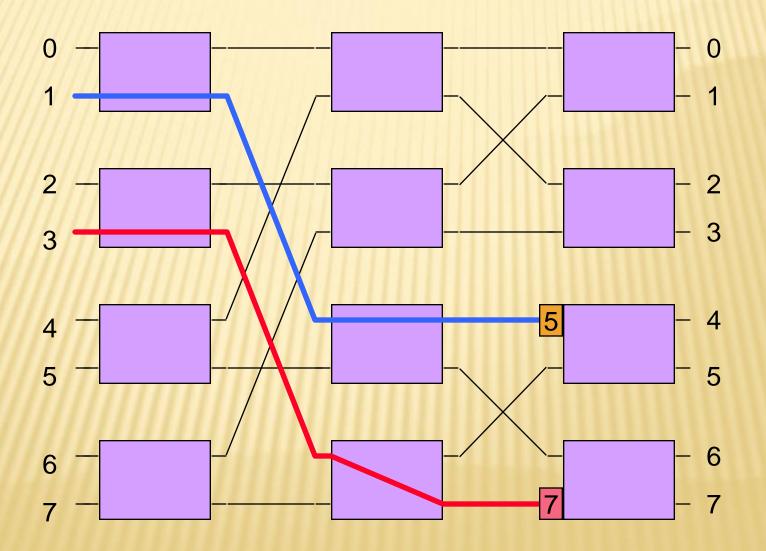

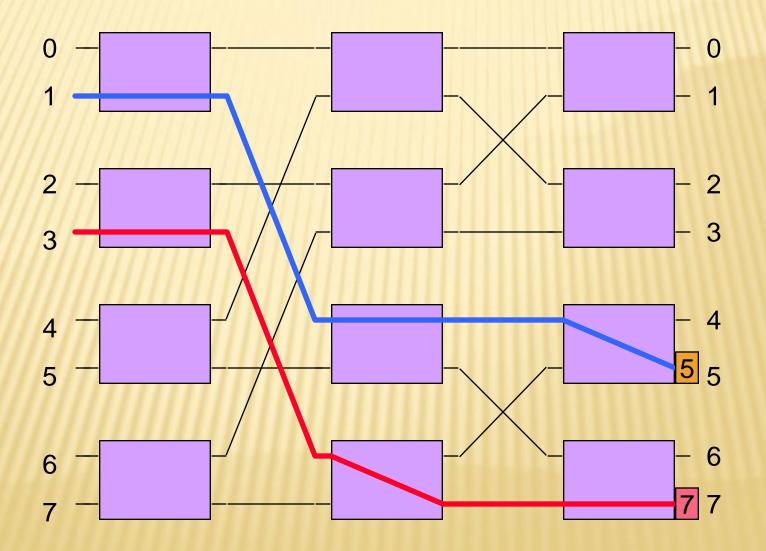

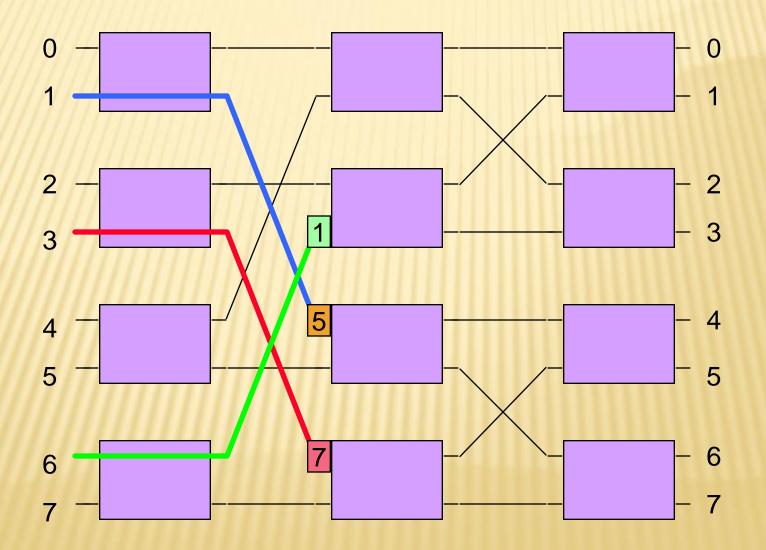

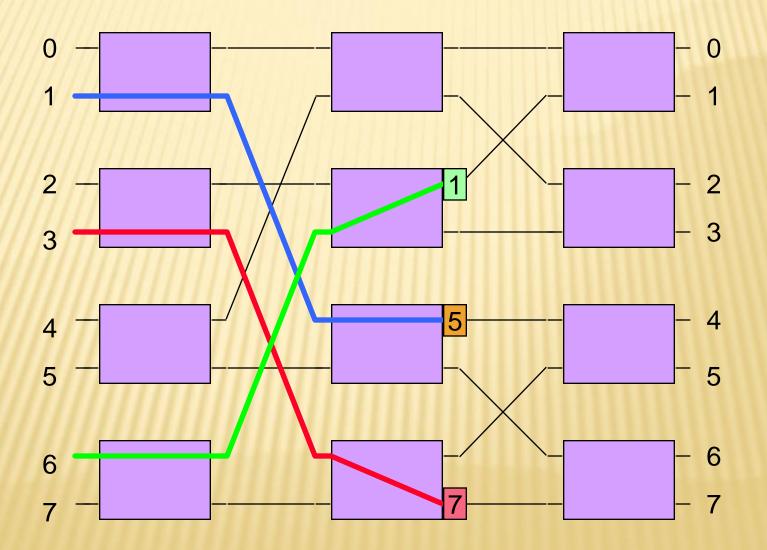

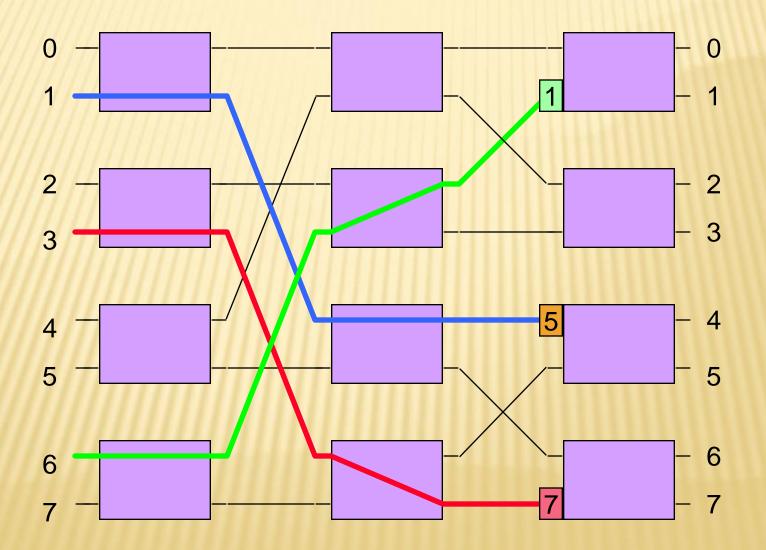

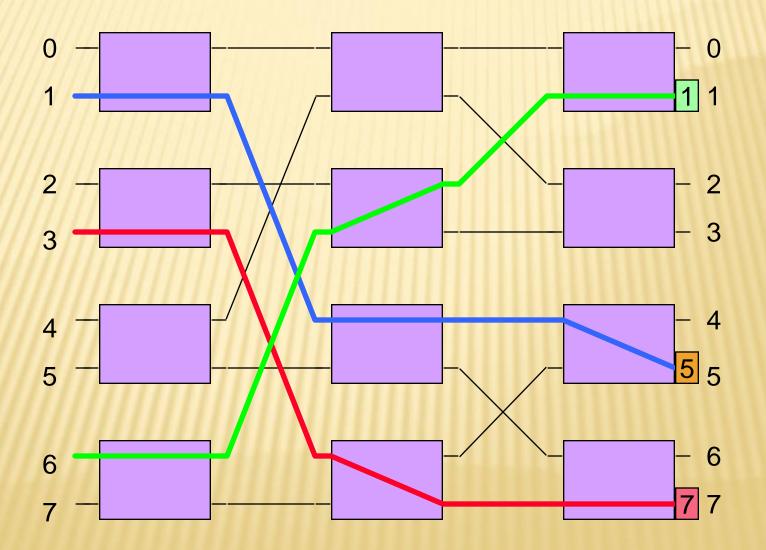

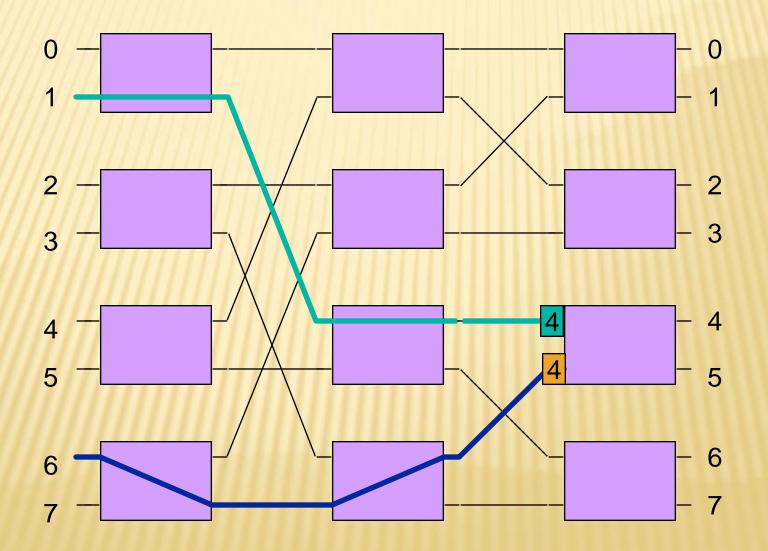

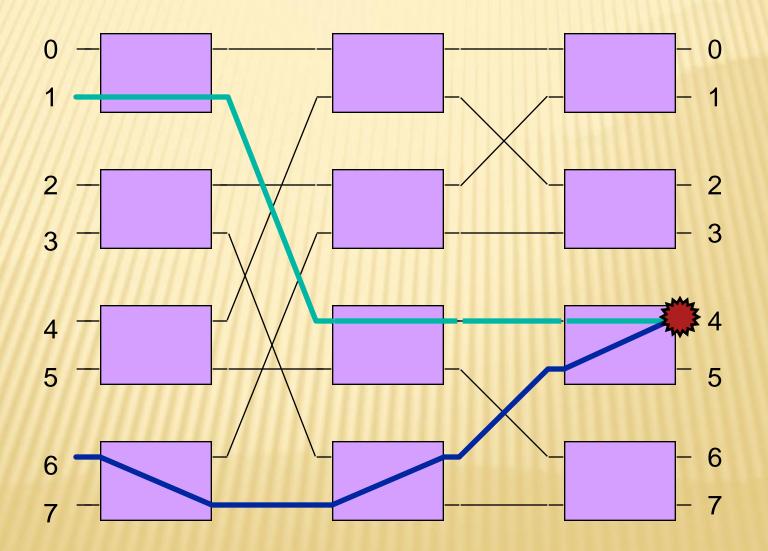

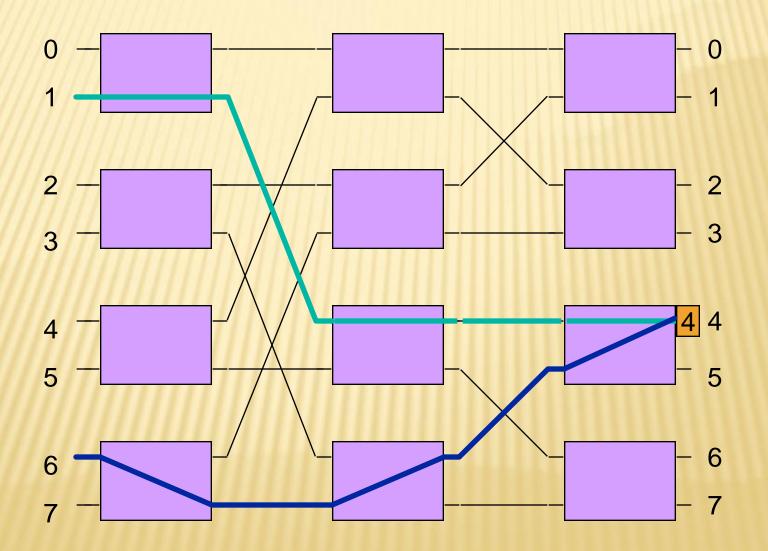

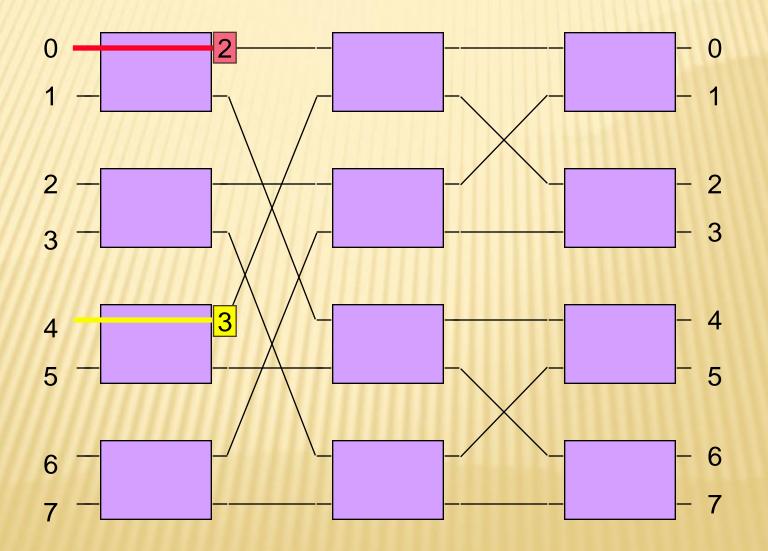

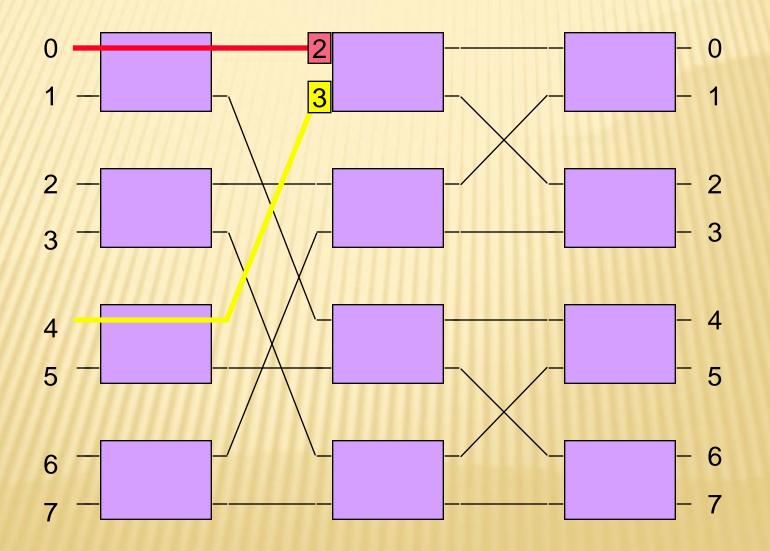

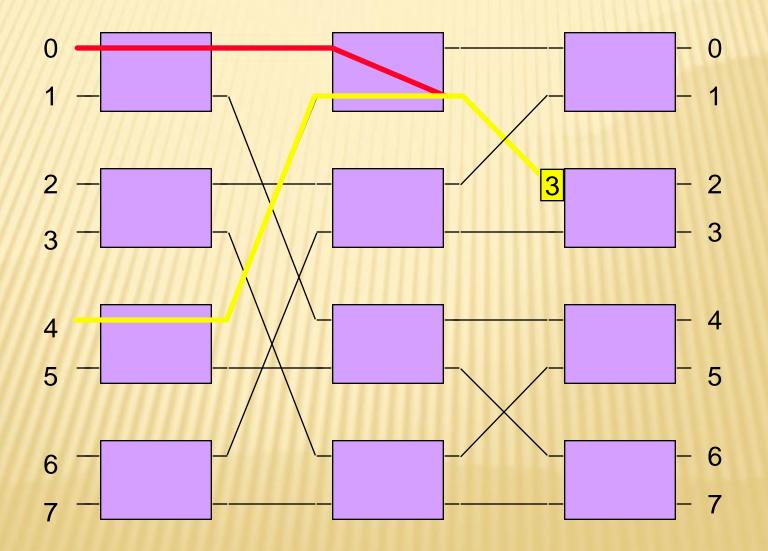

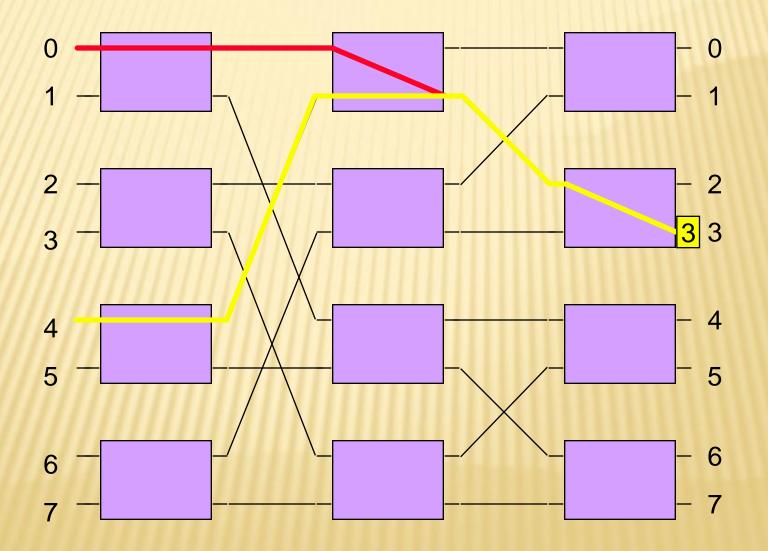

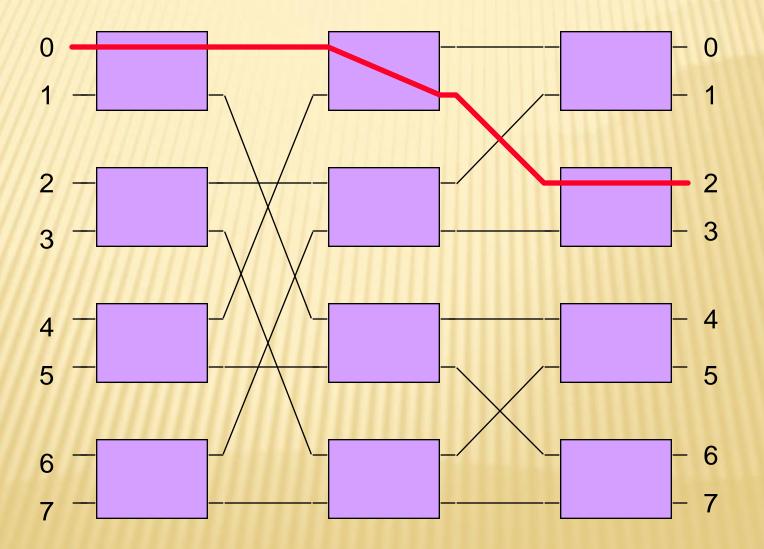

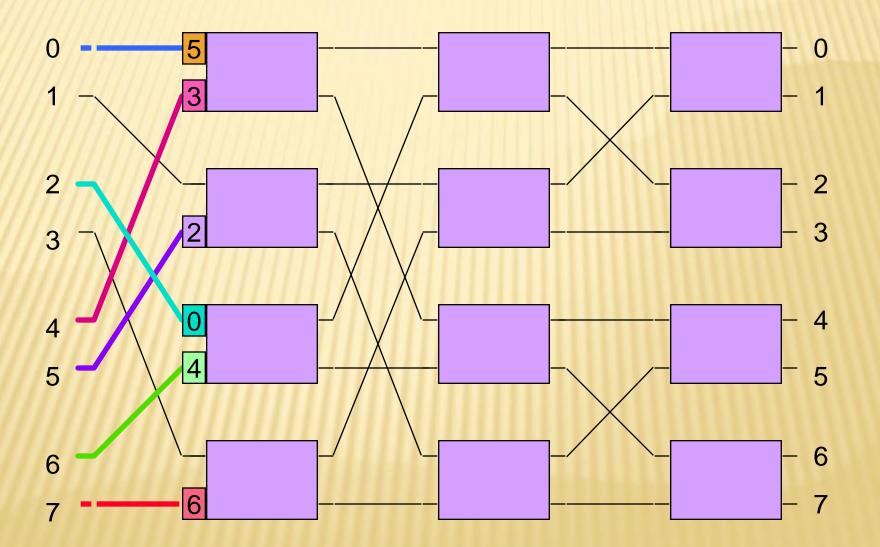

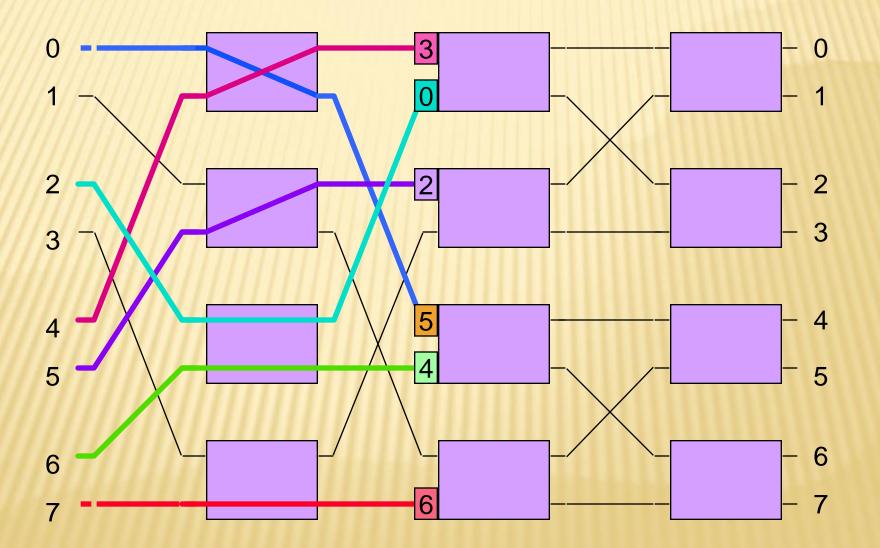

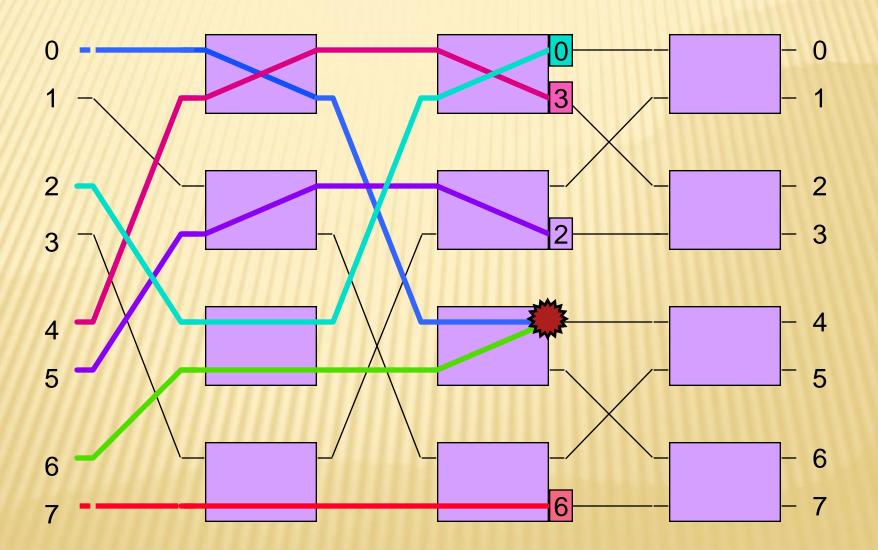

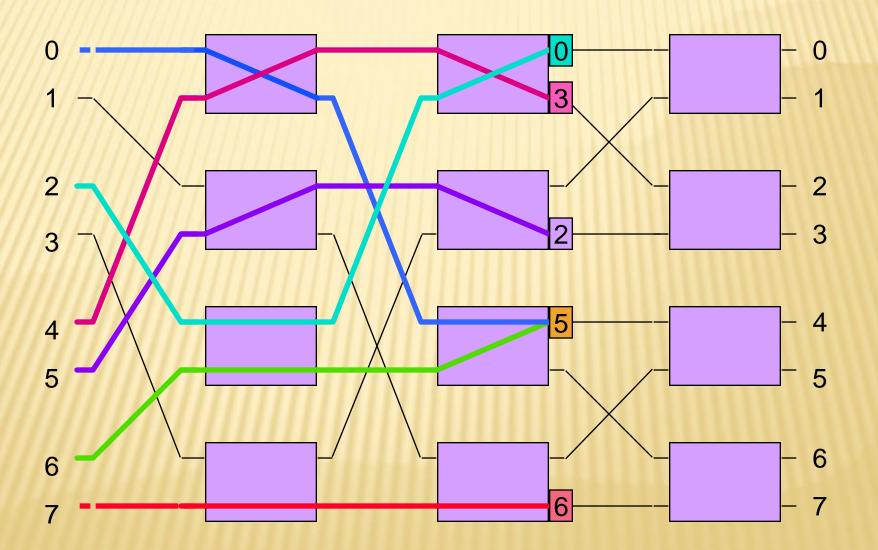

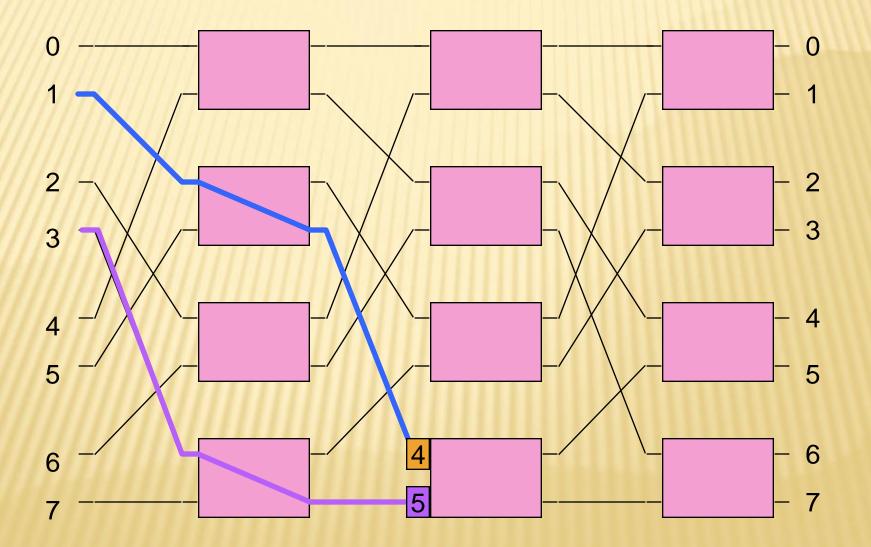

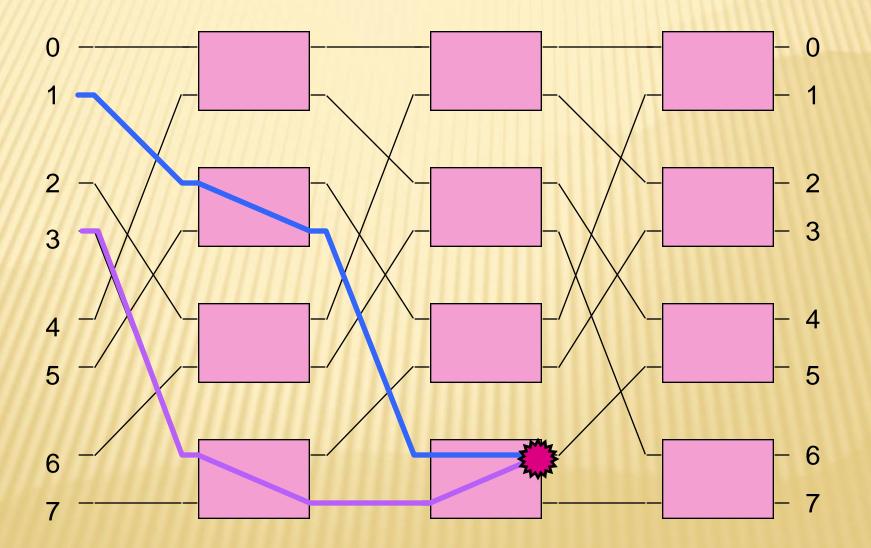

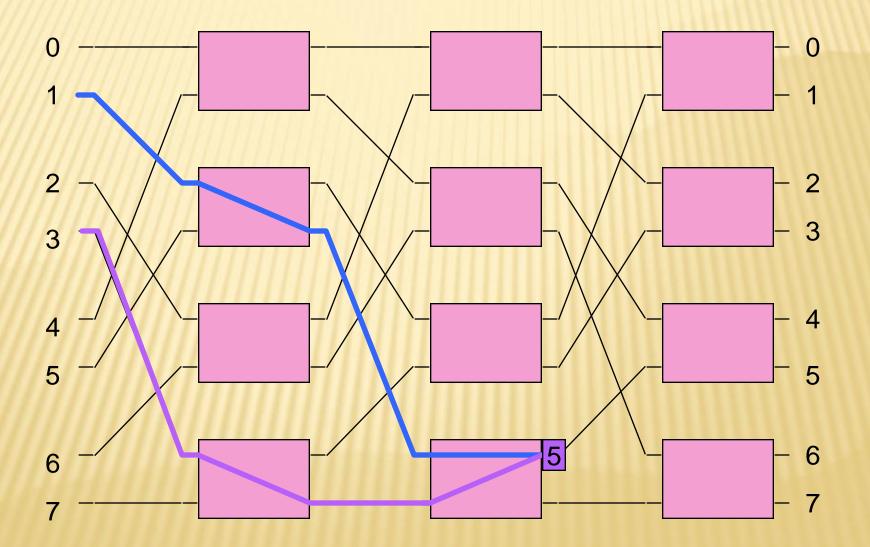

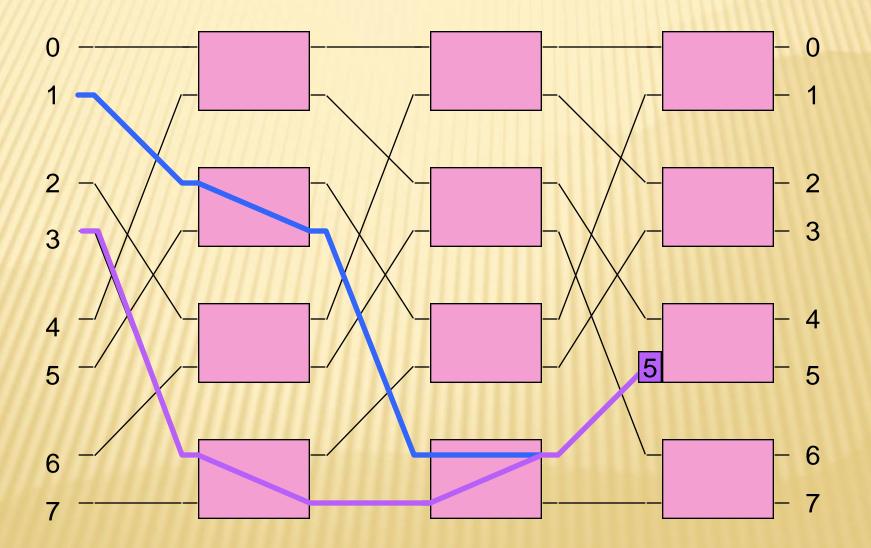

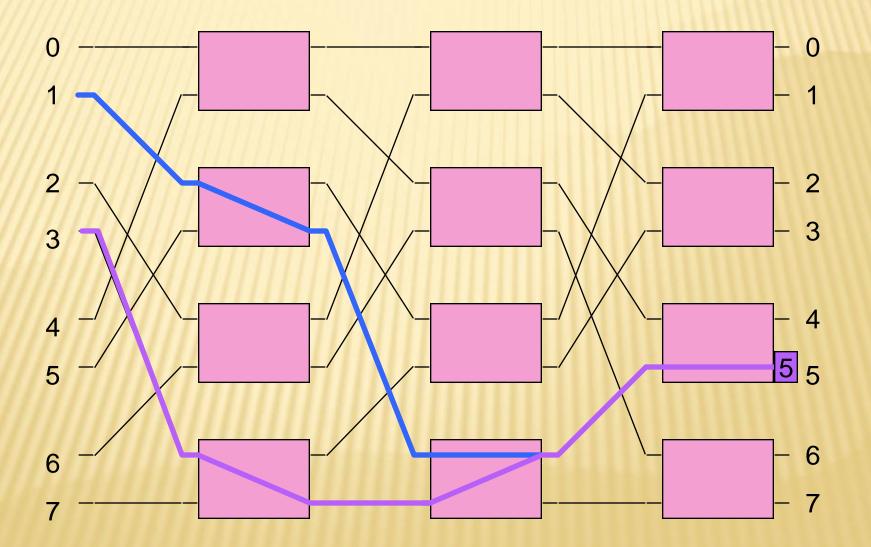

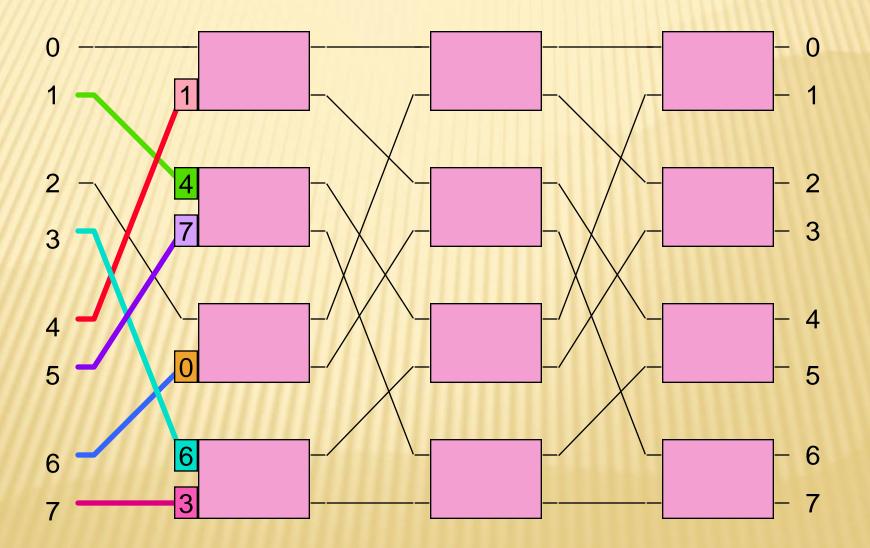

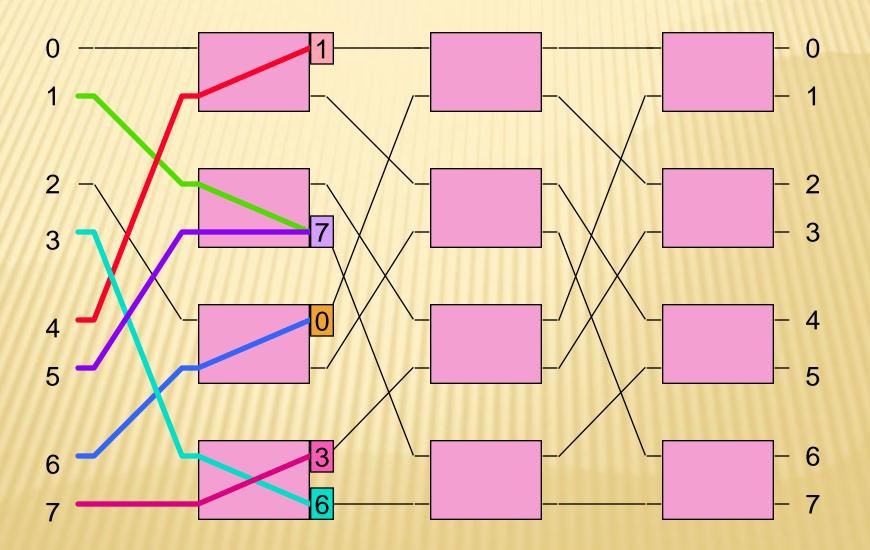

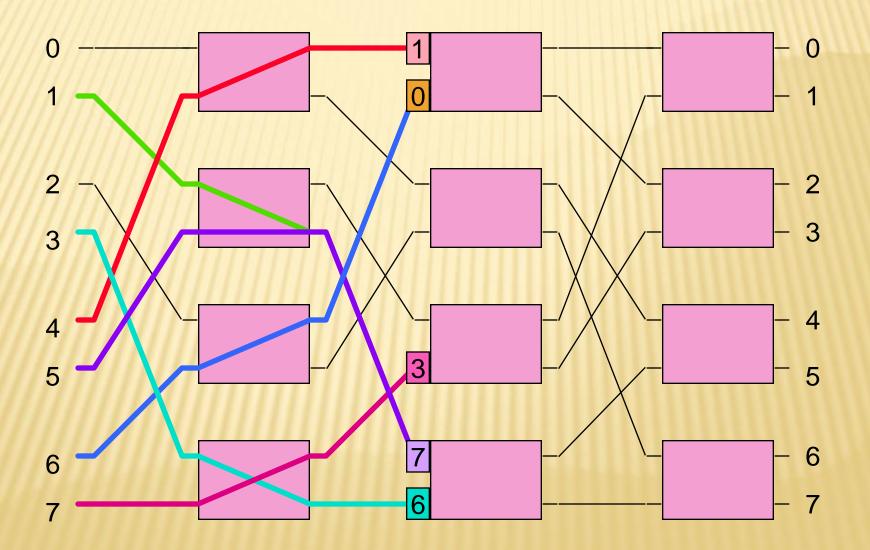

### 8 X 8 DELTA NETWORK

Cell on input port 0 destined for output port 2

#### 8 x 8 DELTA NETWORK

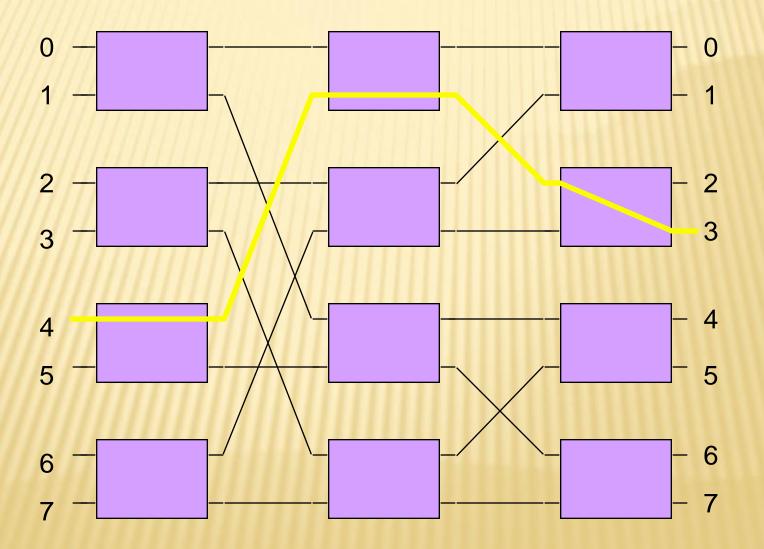

#### Cell on input port 4 destined for output port 3

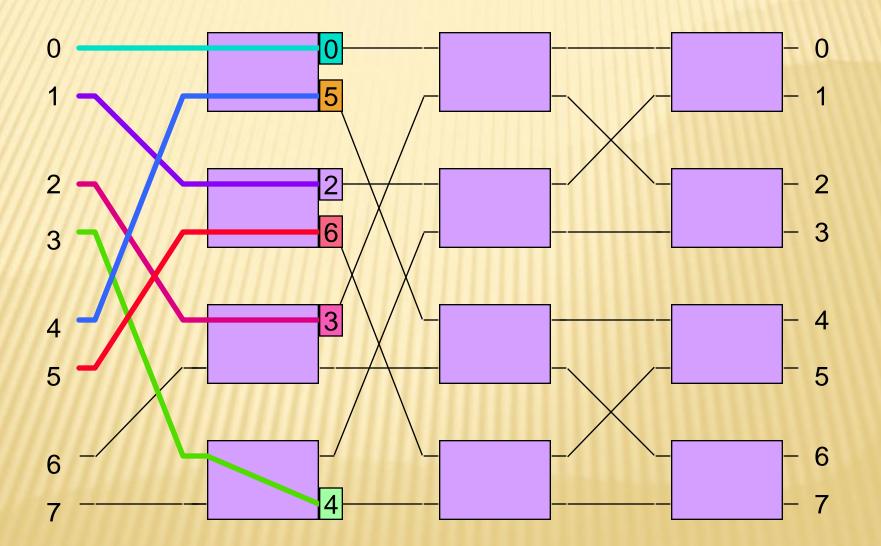

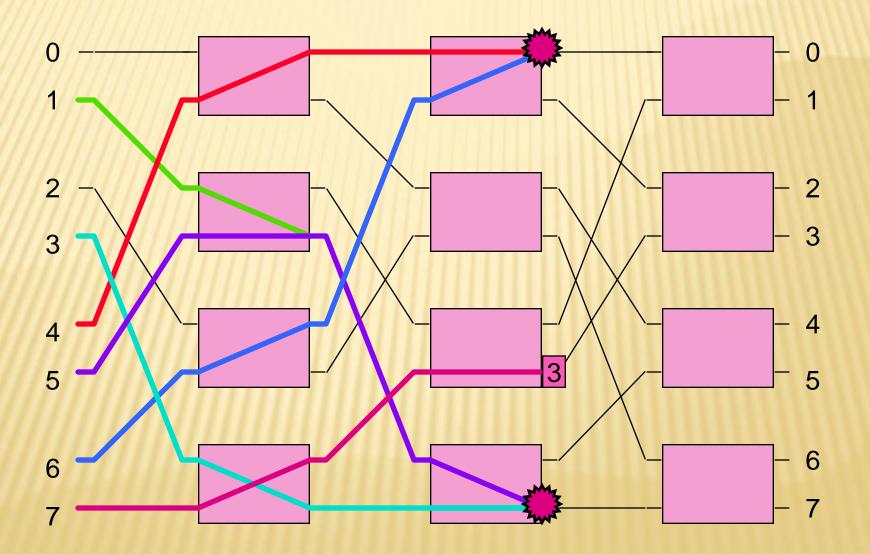

#### INTERNAL BLOCKING

Cell on input port 0 destined for output port 2

Cell on input port 4 destined for output port 3

# **OMEGA NETWORK**

- The <u>omega network</u> is another example of a banyan multistage interconnection network that can be used as a switch fabric

- The omega differs from the delta network in the pattern of interconnections between the stages

- > The omega MIN uses the "perfect shuffle"

# PERFECT SHUFFLE

- The interconnections between stages are defined by the logical "rotate left" of the bits used in the port ids

- **x** Example: 000 ---> 000 ---> 000 ---> 000

- x Example: 001 ---> 010 ---> 100 ---> 001

- × Example: 011 ---> 110 ---> 101 ---> 011

- × Example: 111 ---> 111 ---> 111 ---> 111

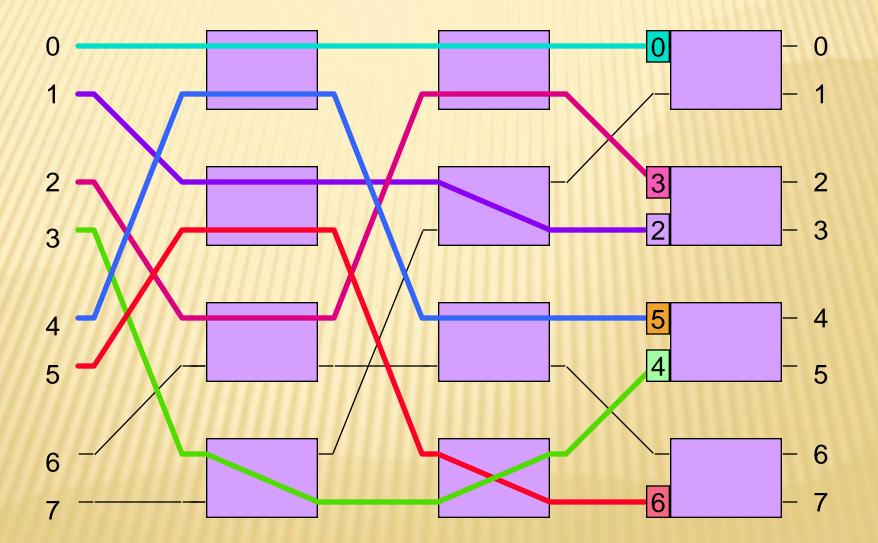

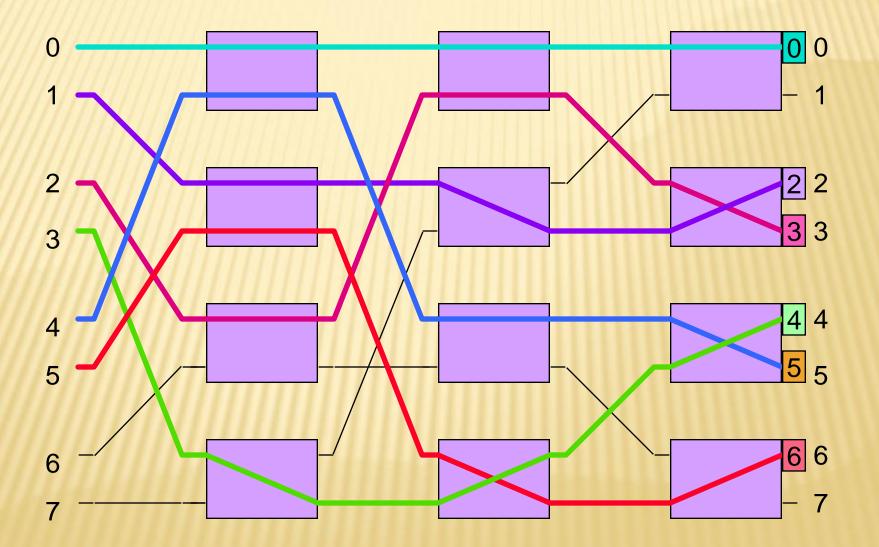

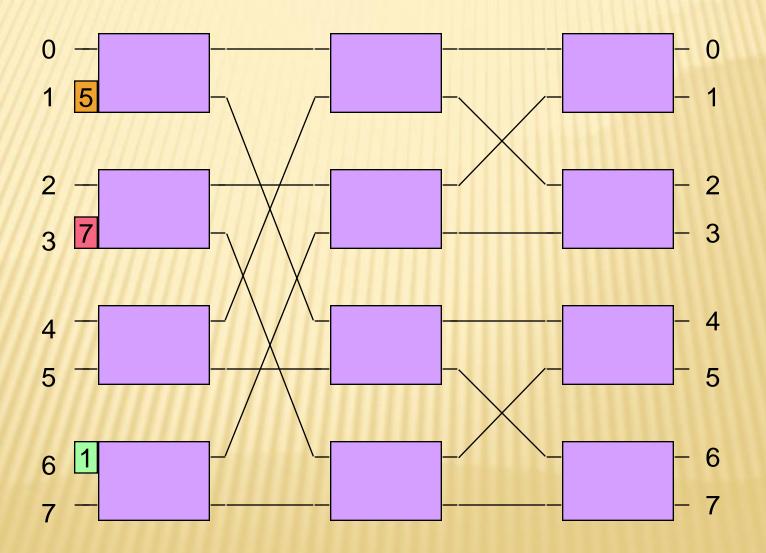

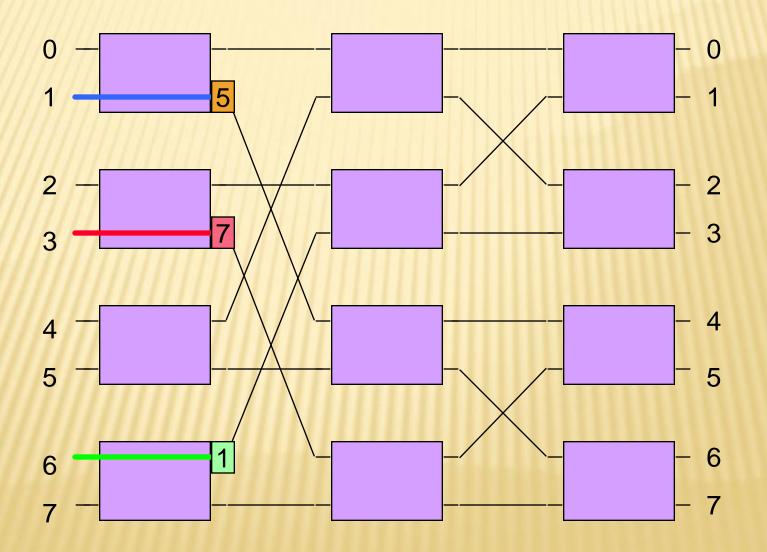

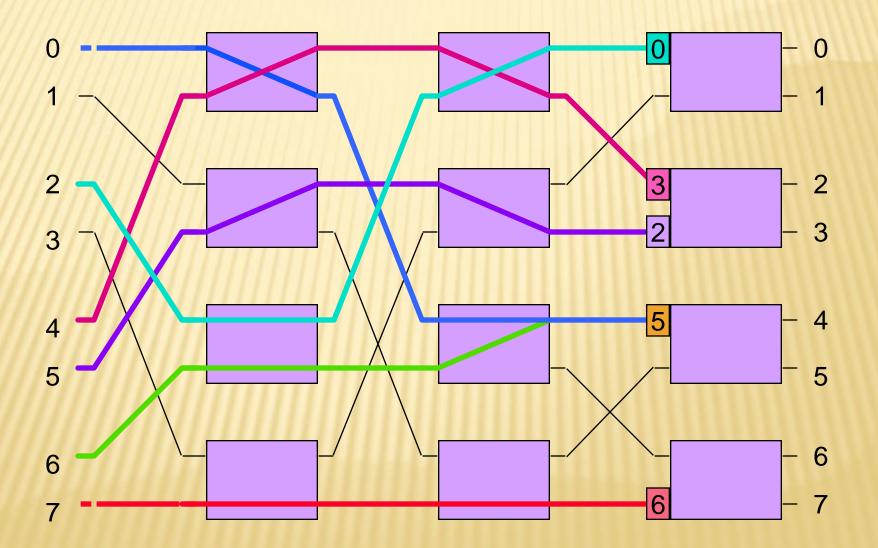

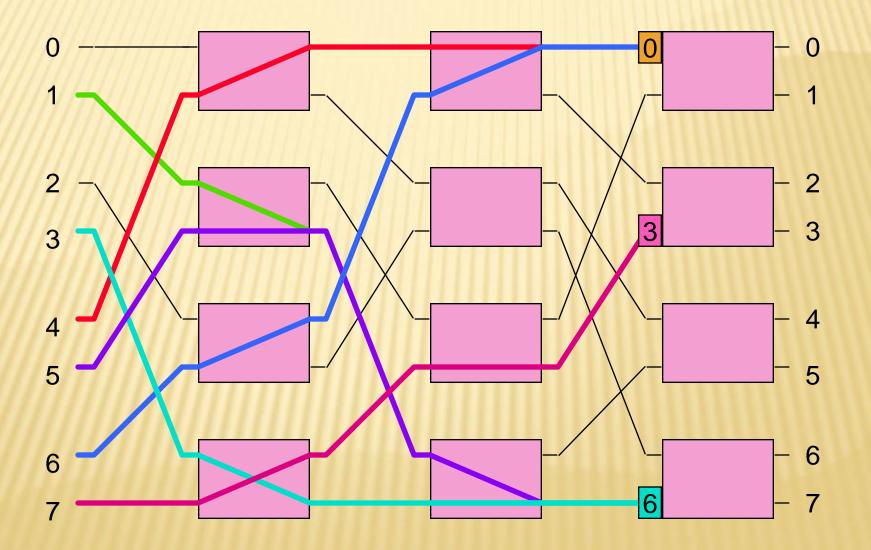

### 8 X 8 OMEGA NETWORK

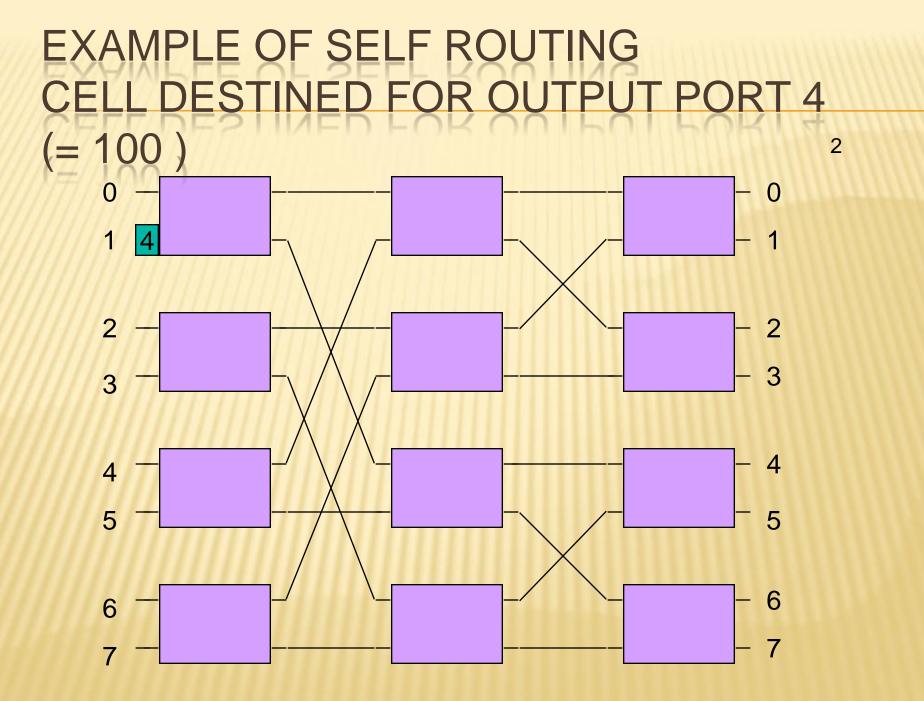

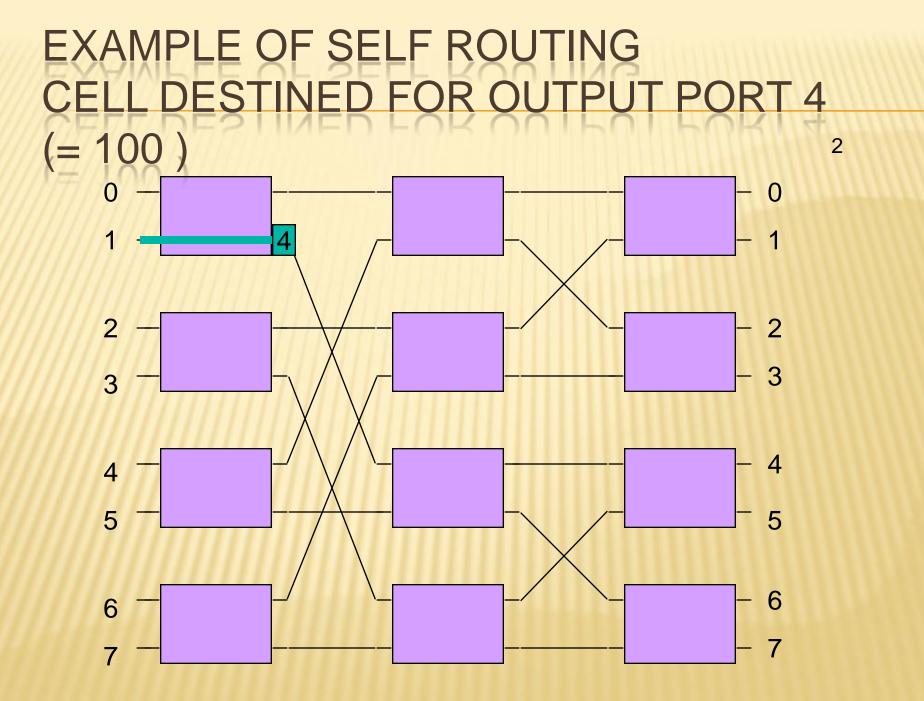

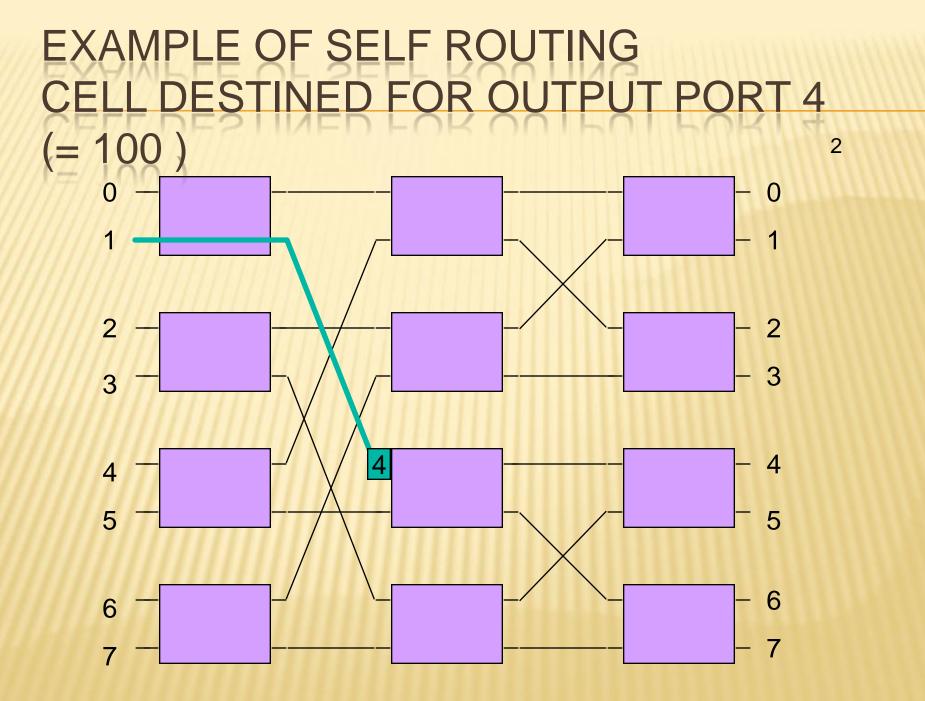

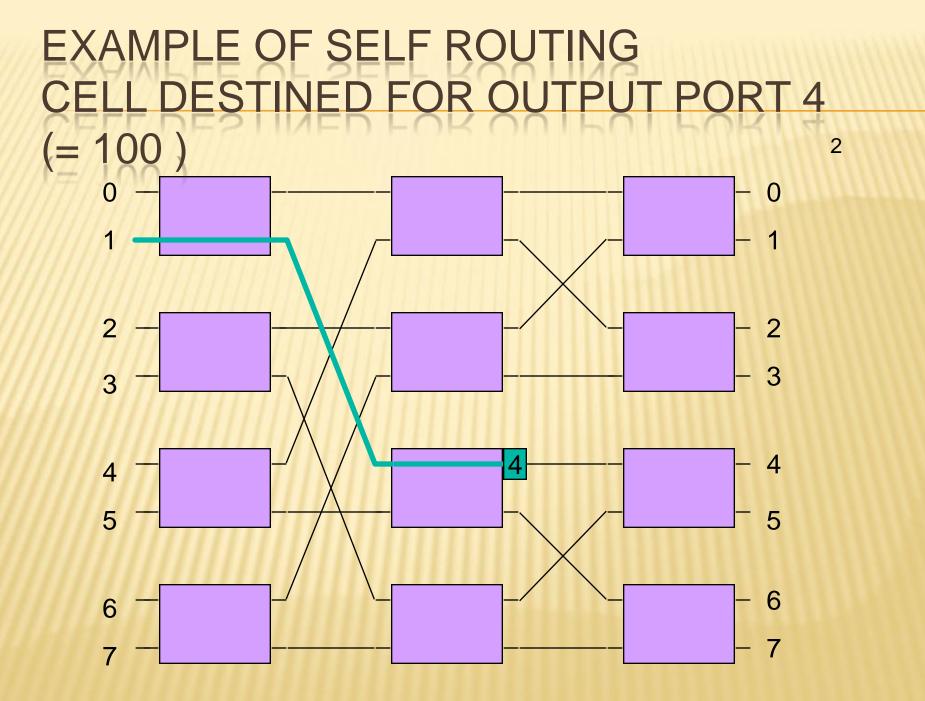

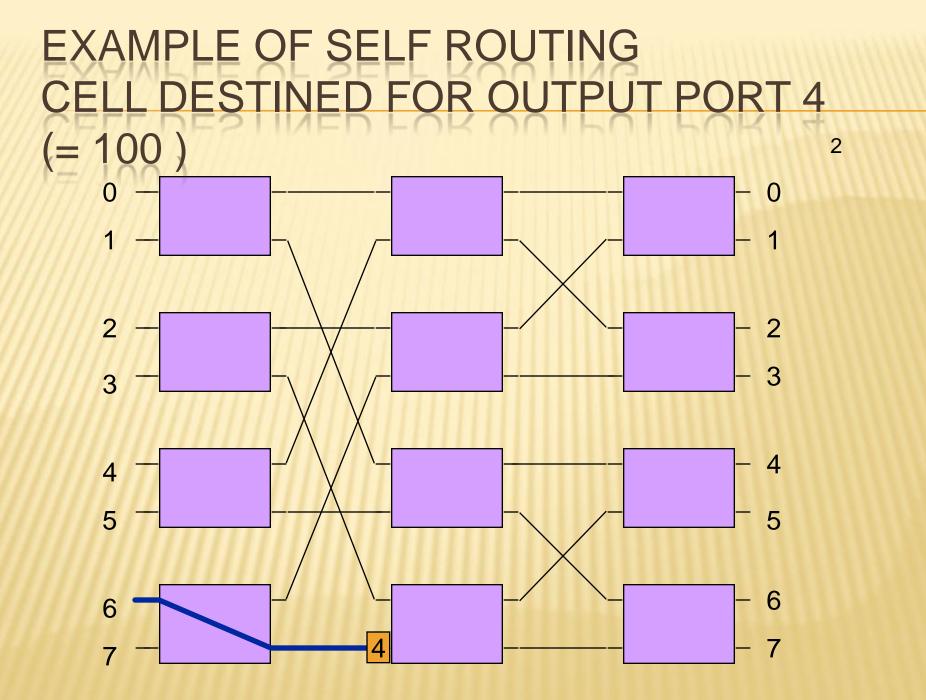

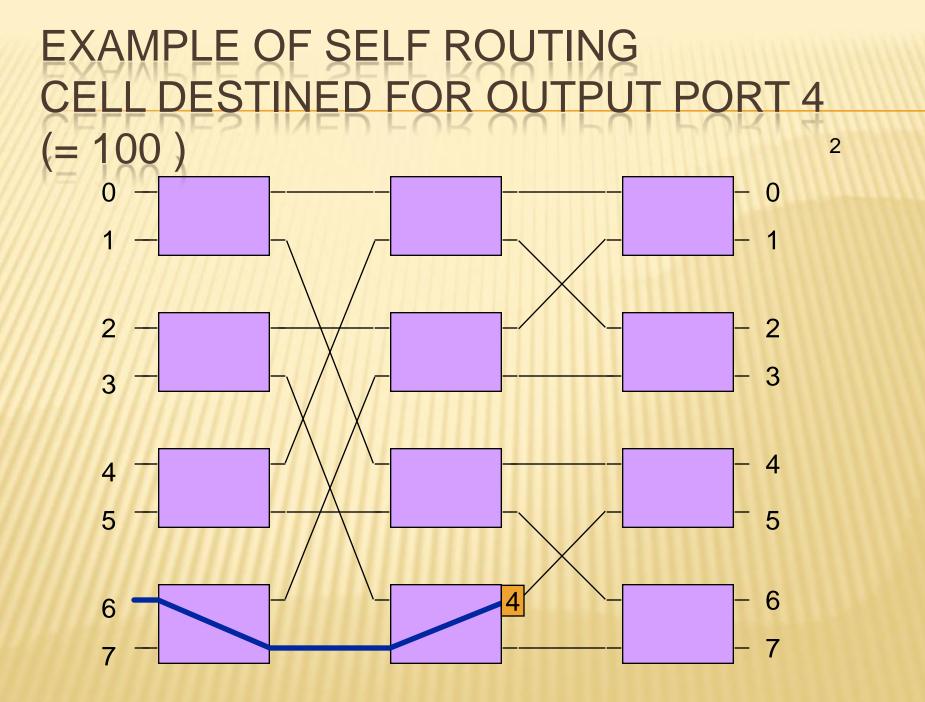

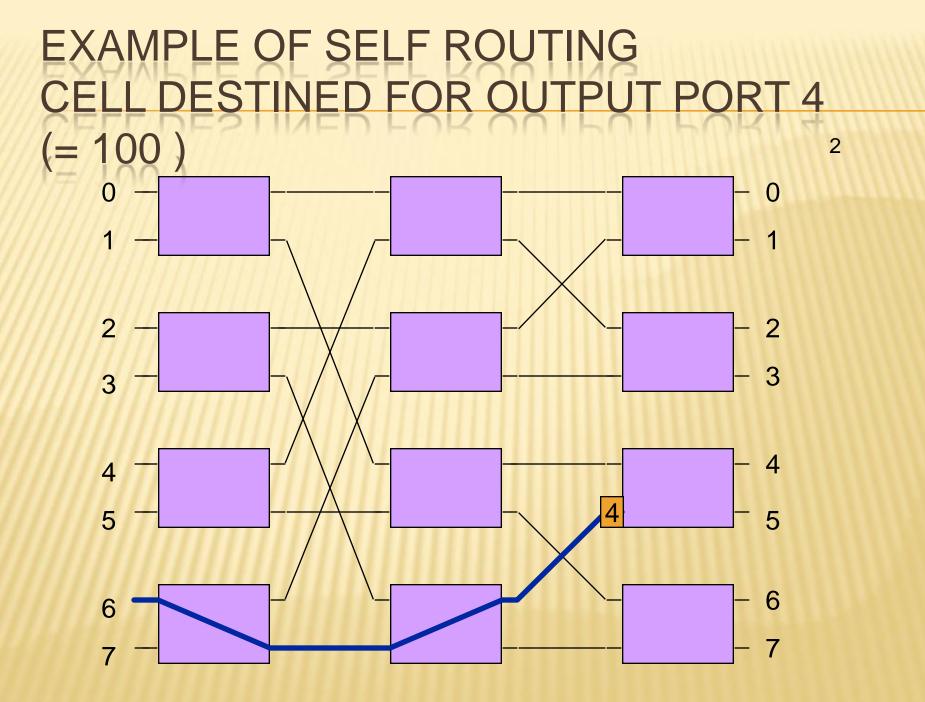

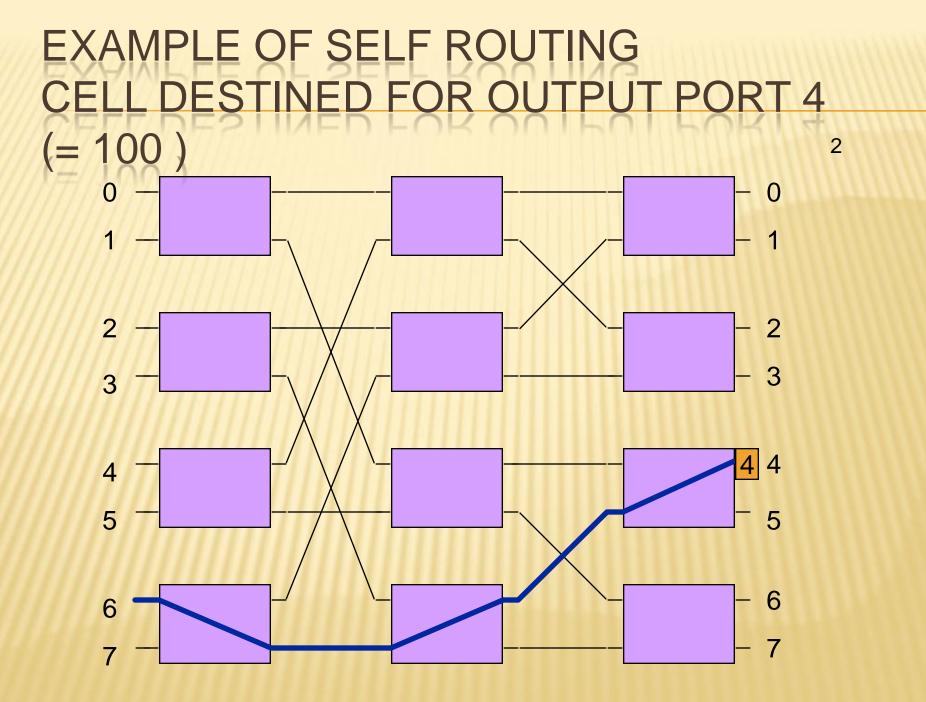

# SELF ROUTING

- > Omega network has <u>self-routing property</u>

- The path for a cell to reach its destination can be determined directly from its <u>routing tag (i.e.,</u> destination port id)

- Stage k of the MIN looks at bit k of the tag

- If <u>bit k is 0</u>, then send cell out <u>upper port</u>

- If <u>bit k is 1</u>, then send cell out <u>lower port</u>

- Works for every possible input port (really!)

# PATH CONTENTION

- The omega network has the problems as the delta network with output port contention and path contention

- Again, the result in a bufferless switch fabric is <u>cell loss</u> (one cell wins, one loses)

- Path contention and output port contention <u>can seriously degrade the achievable</u> <u>throughput of the switch</u>

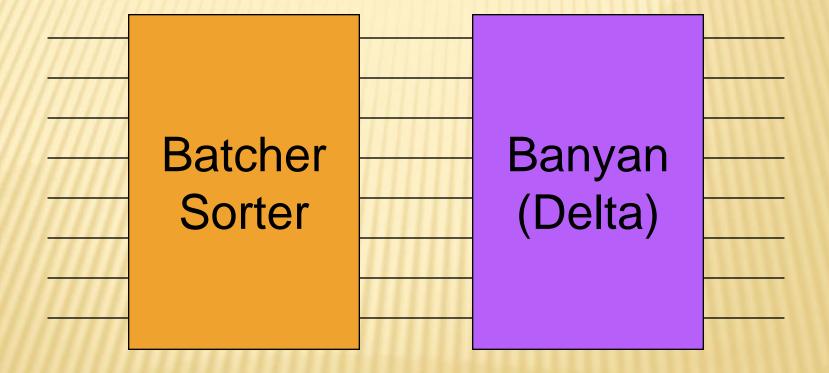

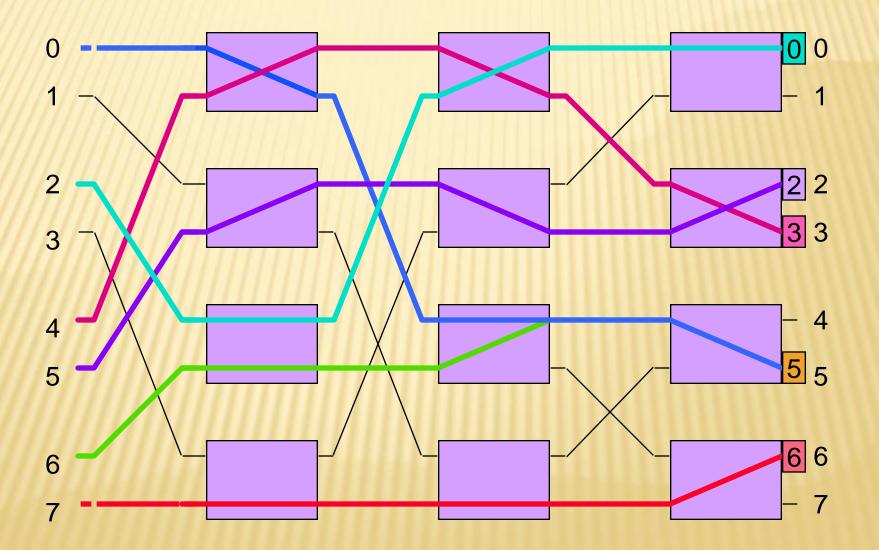

# A SOLUTION: BATCHER SORTER

- One solution to the contention problem is to <u>sort the cells</u> into monotonically increasing order <u>based on desired destination port</u>

- Done using a bitonic sorter called a <u>Batcher</u>

- Places the M cells into gap-free increasing sequence on the first M input ports

- Eliminates duplicate destinations

# **BATCHER-BANYAN**